# LT165

## **Uart TFT LCD Display Controller**

**Specification**

**V1.0A**

## **Version History**

| Version | Date       | Description                                                                                                                                              |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0    | 2025/07/08 | Priliminary Release                                                                                                                                      |

| V1.0A   | 2025/07/17 | <ul> <li>Schematic Modification: Serial port upgrade UART0 Change to<br/>use UART1; added reservation RTP (Resistive Touch Panel)<br/>circuit</li> </ul> |

## Copyright

The copyright of this document belongs to Levetop Semiconductor. If you need to copy, please obtain the license of Levetop Semiconductor in advance. Although the information contained in this document has been proofread, Levetop Semiconductor does not assume any responsibility for the specifications of the document. The application mentioned in the document is for reference only. Levetop Semiconductor does not guarantee that such applications do not require further modify. Levetop Semiconductor reserves the right to change its product specifications or documents without prior notice. For the latest product information, please visit our website: <a href="https://www.levetop.cn">www.levetop.cn</a>

## **Contents**

| Ve  | rsion Histo | ry                                 | 2  |  |

|-----|-------------|------------------------------------|----|--|

| Сс  | pyright     |                                    | 2  |  |

| Сс  | ntents      |                                    | 3  |  |

| Fic | aure List   |                                    | 16 |  |

| •   | Table List2 |                                    |    |  |

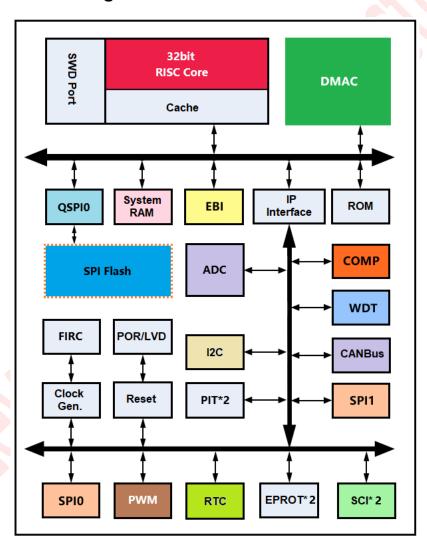

| 1.  |             | troduction                         |    |  |

| ٠.  |             | duction                            |    |  |

|     |             | nal Block Diagram                  |    |  |

|     |             | ures                               |    |  |

|     | 1.3.1.      | 32bits RISC Core                   |    |  |

|     | 1.3.2.      | 32K Bytes SRAM                     |    |  |

|     | 1.3.3.      | 6K Bytes ROM                       |    |  |

|     | 1.3.4.      | 2K Byte Cache                      |    |  |

|     | 1.3.5.      | External Bus Interface (EBI )      |    |  |

|     | 1.3.6.      | DMA Module                         |    |  |

|     | 1.3.7.      | RESET Module                       |    |  |

|     | 1.3.8.      | Programmable Interrupt Timer (PIT) | 30 |  |

|     | 1.3.9.      | Watch Dog Timer (WDT)              | 30 |  |

|     | 1.3.10.     | Real Time Clock (RTC)              | 30 |  |

|     | 1.3.11.     | EPORT                              | 31 |  |

|     | 1.3.12.     | SPI Module                         | 31 |  |

|     | 1.3.13.     | SSI / QSPI Module                  | 31 |  |

|     | 1.3.14.     | SCI / UART Module                  | 31 |  |

|     | 1.3.15.     | CANBus Controller                  | 32 |  |

|     | 1.3.16.     | PWM Module                         | 33 |  |

|     | 1.3.17.     | ADC Module                         | 33 |  |

|     | 1.3.18.     | I2C Module                         | 33 |  |

|     | 1.3.19.     | Analog Comparator                  | 34 |  |

|     | 1.3.20.     | Touch Sensor                       | 34 |  |

|     | 1.3.21.     | Power Management Unit (PMU)        | 34 |  |

|     | 1.3.22.     | Voltage Detector                   | 34 |  |

|     | 1.3.23.     | Internal Oscillator                | 34 |  |

|     | 1.3.24.     | External Crystal Oscillator        | 34 |  |

|     | 1.4. Syste  | em Block Diagram                   | 35 |  |

|     | 1.5. Syste  | em Memory Map                      | 35 |  |

|     |             |                                    |    |  |

|    | 1.5  | 5.1. Introduction                           | 35 |

|----|------|---------------------------------------------|----|

|    | 1.5  | 5.2. Memory Address Map                     | 36 |

| 2. | Sign | nal Description                             | 38 |

|    | 2.1. | Pin Assignment                              | 38 |

|    | 2.2. | Signal Properties Summary                   | 40 |

|    | 2.3. | Signal Description                          | 42 |

|    | 2.4. | LT165A vs. LT165B                           | 49 |

| 3. | Hard | dware Interface                             | 50 |

|    | 3.1. | Host Communication Interface                | 50 |

|    | 3.2. | TFT LCD Panel Interface                     | 50 |

|    | 3.3. | QSPI Interface                              | 51 |

|    | 3.4. | LCD Touch Panel Interface                   | 51 |

|    | 3.5. | Clock Interface                             | 52 |

|    | 3.6. | Can Bus Interface                           | 52 |

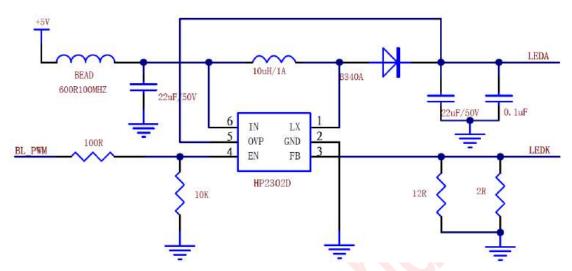

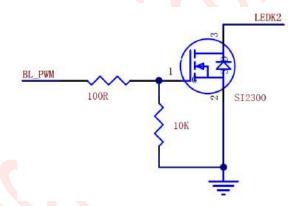

|    | 3.7. | LCD Backlight Control Circuit               | 53 |

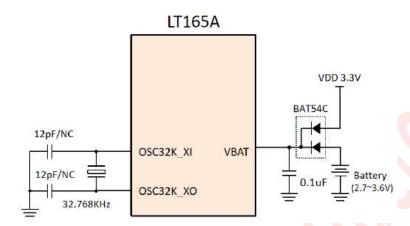

|    |      | Real Time Clock (RTC)                       |    |

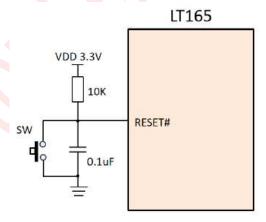

|    | 3.9. | Reset Interface                             | 54 |

| 4. | Emb  | pedded Interrupt Controller (EIC)           | 55 |

|    |      | Introduction                                |    |

|    |      | Features                                    |    |

|    |      | Memory Map and Registers                    |    |

|    |      | 3.1. Memory Map                             |    |

|    | 4.3  | 3.2. Registers                              | 57 |

|    | 4.4. | Function Description                        | 63 |

|    | 4.4  | 4.1. Interrupt Handling Without Confliction | 63 |

|    | 4.4  | 4.2. Interrupt With Confliction             | 64 |

|    | 4.4  | 4.3. Pend Trap Function                     | 65 |

|    | 4.5. | Interrupts                                  | 65 |

| 5. | RISC | C Core Introduction                         | 69 |

|    | 5.1. | Features                                    | 69 |

|    | 5.2. | Microarchitecture Summary                   | 69 |

|    | 5.3. | Programming Model                           | 70 |

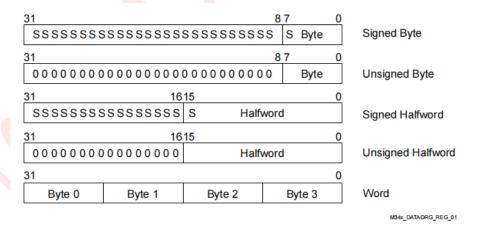

|    | 5.4. | Data Format Summary                         | 71 |

|    | 5.5. | Operand Addressing Capabilities             | 72 |

|    | 5.6. | Instruction Set Overview                    | 72 |

| 6. | Emb  | oedded Programmable Timer (EPT)             | 75 |

|    |      |                                             |    |

|    | 6.1. Intro | duction                                                                   | 75  |

|----|------------|---------------------------------------------------------------------------|-----|

|    | 6.2. Men   | nory Map and Registers                                                    | 75  |

|    | 6.2.1.     | Memory Map                                                                | 75  |

|    | 6.2.2.     | Registers                                                                 | 76  |

|    | 6.3. Fund  | ction Description                                                         | 79  |

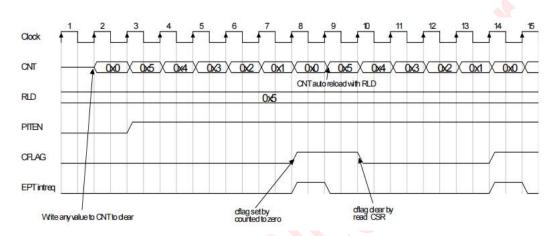

|    | 6.3.1.     | Count Timing                                                              | 79  |

| 7. | System     | Integration Module (SIM)                                                  | 80  |

|    | 7.1. Intro | duction                                                                   | 80  |

|    | 7.2. Feat  | ures                                                                      | 80  |

|    | 7.3. Mod   | es of Operation                                                           | 81  |

|    | 7.3.1.     | Normal Mode                                                               |     |

|    | 7.3.2.     | Debug Mode                                                                | 81  |

|    | 7.4. Men   | nory Map                                                                  | 81  |

|    | 7.5. Reg   | ister Descriptions                                                        | 82  |

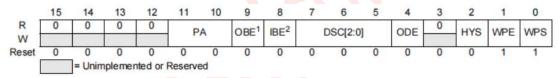

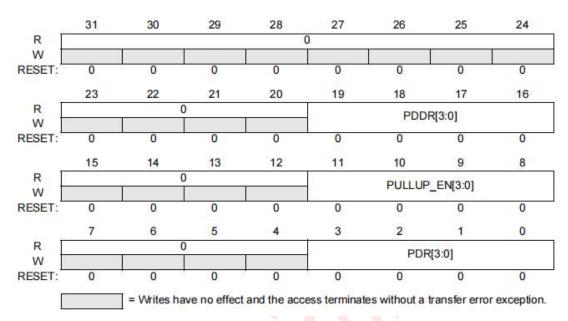

|    | 7.5.1.     | Pad Configuration Registers (SIM_PCR)                                     |     |

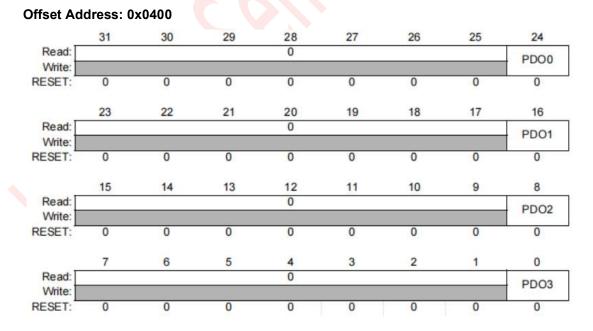

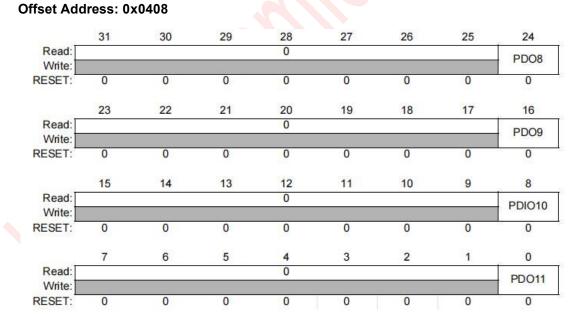

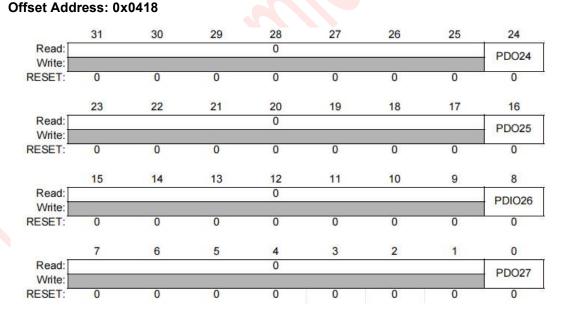

|    | 7.5.2.     | GPIO Pin Data Output Registers (SIM_GPDO0_3 ~ SIM_GPDO28_31)              | 86  |

|    | 7.5.3.     | GPIO Pin Data Input Registers (SIM_GPDI0_3 ~ SIM_GPDI_28_31)              | 90  |

|    | 7.5.4.     | Parallel GPIO Pin Data Output Register (SIM_PGPDO0)                       | 95  |

|    | 7.5.5.     | Parallel GPIO Pin Data Input Register (SIM_PGPDI0)                        | 96  |

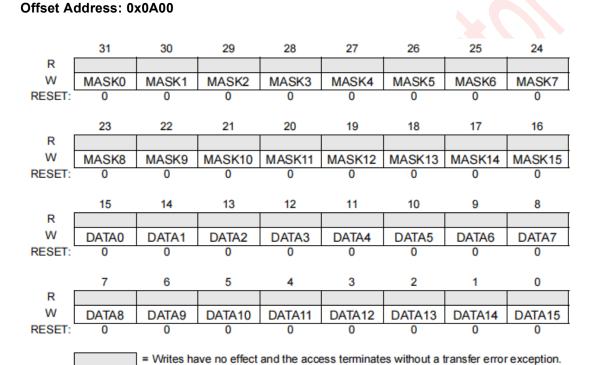

|    | 7.5.6.     | Masked Parallel GPIO Pin Data Output Register (SIM_MPGPDO0 - SIM_MPGPDO1) | 97  |

|    | 7.5.7.     | WKUPC — Wakeup Configuration Register                                     |     |

|    | 7.5.8.     | QSPIXIPMCFR — QSPI XIP Mode Configuration Register                        | 101 |

|    | 7.5.9.     | QSPILKEYR — QSPI 32bit Key Register                                       | 102 |

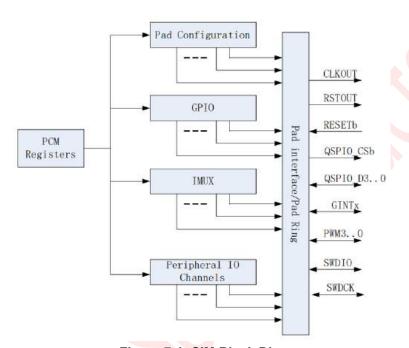

|    | 7.6. Fund  | ctional Description                                                       | 102 |

|    | 7.6.1.     | Pad Configuration                                                         | 102 |

|    | 7.6.2.     | GPIO Operation                                                            | 102 |

| 8. | Clock ar   | nd Power Control Module (CLKM)                                            | 103 |

|    | 8.1. Ove   | rview                                                                     | 103 |

|    | 8.2. Feat  | rures                                                                     | 103 |

|    | 8.3. Cloc  | k Structure                                                               | 104 |

|    | 8.4. Cloc  | k Source Select                                                           | 104 |

|    | 8.4.1.     | Low-Power Options                                                         | 104 |

|    | 8.5. Men   | nory Map and Registers                                                    |     |

|    | 8.5.1.     | Module Memory Map                                                         |     |

|    | 8.5.2.     | Register Description                                                      |     |

|    | 8.6. Fund  | ctional Description                                                       | 121 |

|     | 8.    | 6.1.    | Turning On PLL                                                      | 121 |

|-----|-------|---------|---------------------------------------------------------------------|-----|

|     | 8.    | 6.2.    | The Frequency of PLL Measurement                                    | 121 |

|     | 8.    | 6.3.    | The Frequency of 128KHz Measurement                                 | 122 |

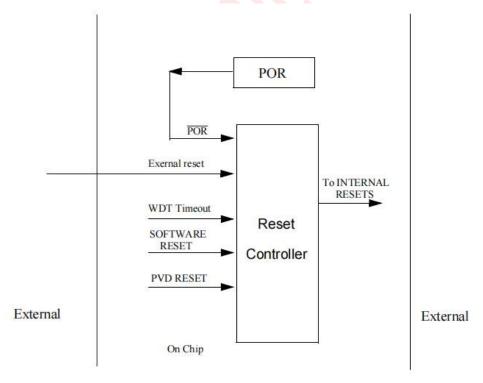

| 9.  | Res   | et Co   | ntroller Module (RCM)                                               | 123 |

|     | 9.1.  | Overv   | iew                                                                 | 123 |

|     | 9.2.  | Featu   | res                                                                 | 123 |

|     | 9.3.  | Block   | Diagram                                                             | 123 |

|     | 9.4.  | Memo    | ory Map and Registers                                               | 124 |

|     | 9.    | 4.1.    | Reset Test Register                                                 |     |

|     | 9.    | 4.2.    | Reset Status Register                                               | 125 |

|     | 9.    | 4.3.    | Reset Control Register                                              | 126 |

|     | 9.5.  | Functi  | onal Description                                                    | 126 |

|     | 9.    | 5.1.    | Reset Sources                                                       | 126 |

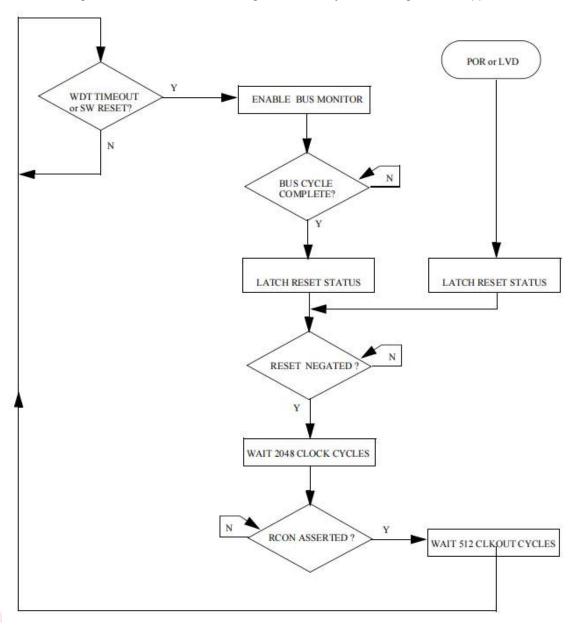

|     | _     | 5.2.    | Reset Control Flow                                                  |     |

| 10. | Stat  | ic Rar  | ndom Access Memory (SRAM)                                           | 129 |

|     |       |         | uction                                                              |     |

|     |       |         | s of Operation                                                      |     |

|     | 10.3. | Low-F   | Power Modes                                                         | 129 |

|     |       |         | Operation                                                           |     |

|     | 10.5. | Interru | ıpts                                                                | 129 |

| 11. |       |         | odule (CACHEM)                                                      |     |

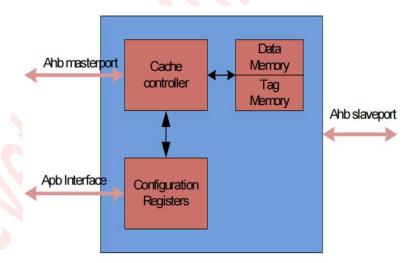

|     |       |         | uction                                                              |     |

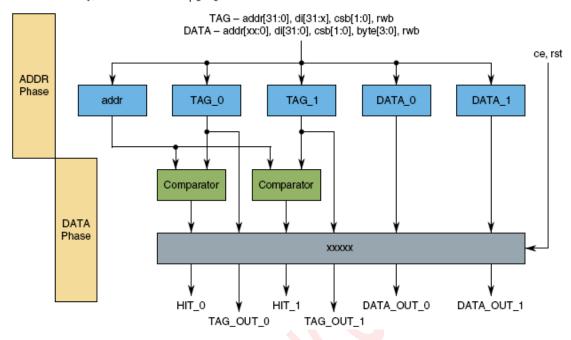

|     |       |         | Diagram                                                             |     |

|     |       |         | pry Map/Register Definition                                         |     |

|     |       |         | ter Description                                                     |     |

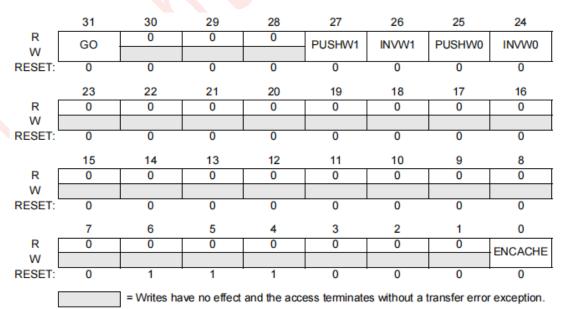

|     |       | 1.4.1.  | Cache Control Register (LMEM_CCR)                                   |     |

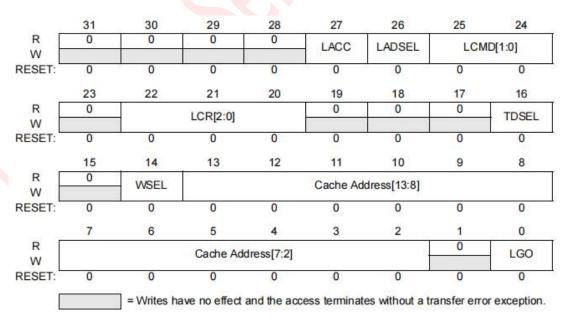

|     | 1     | 1.4.2.  | Cache Line Control Register (LMEM_CLCR)                             |     |

|     | 1     | 1.4.3.  | Cache Search Address Register (LMEM_CSAR)                           |     |

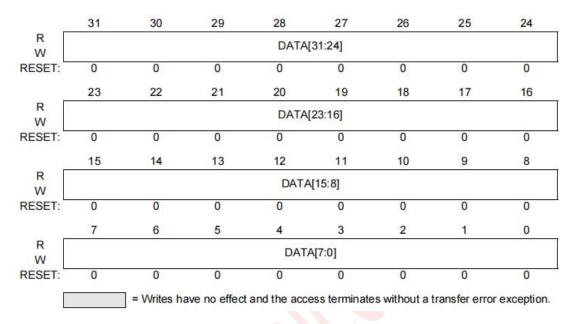

|     | 11    | 1.4.4.  | Cache Read/Write Value Register (LMEM_CCVR)                         | 136 |

|     | 11    | 1.4.5.  | Cache Access Register(LMEM_ACRG)                                    | 137 |

|     | 1′    | 1.4.6.  | Cache Page Invalidation Base Address Register (LMEM_PAGE_INV_BADDR) | 138 |

|     | 11    | 1.4.7.  | Cache Page Invalidation Base Size Register (LMEM_PAGE_INV_SIZE)     | 139 |

|     | 11    | 1.4.8.  | Cache Clock Enable Register (LMEM_CACHE_CLK_EN)                     | 140 |

|     | 11.5. | Cache   | Function                                                            | 140 |

|     | 11.6. | Cache   | e Control                                                           | 142 |

|     | 11    | 1.6.1.  | Cache Set Commands                                                  | 142 |

|     | 1′    | 1.6.2.  | Cache Line Commands                                                 | 143 |

| 12 | . Crossbar   | r Switch (XBAR)                     | 145 |

|----|--------------|-------------------------------------|-----|

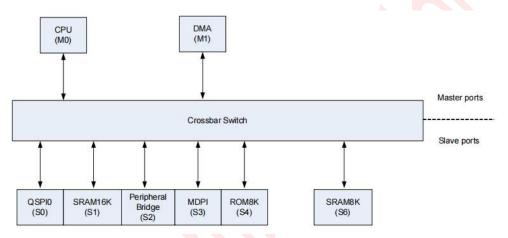

|    | 12.1. Introd | duction                             | 145 |

|    | 12.1.1.      | Overview                            | 145 |

|    | 12.1.2.      | Features                            | 145 |

|    | 12.2. Mem    | ory Map and Registers               | 146 |

|    | 12.2.1.      | Register Summary                    | 146 |

|    | 12.2.2.      | XBAR Register Descriptions          | 147 |

|    | 12.3. Func   | tion                                | 151 |

|    | 12.3.1.      | General Operation                   | 151 |

|    | 12.3.2.      | Register Coherency                  |     |

|    | 12.3.3.      | Arbitration                         |     |

|    | 12.3.4.      | Priority Assignment                 | 153 |

|    |              | lization/Application information    |     |

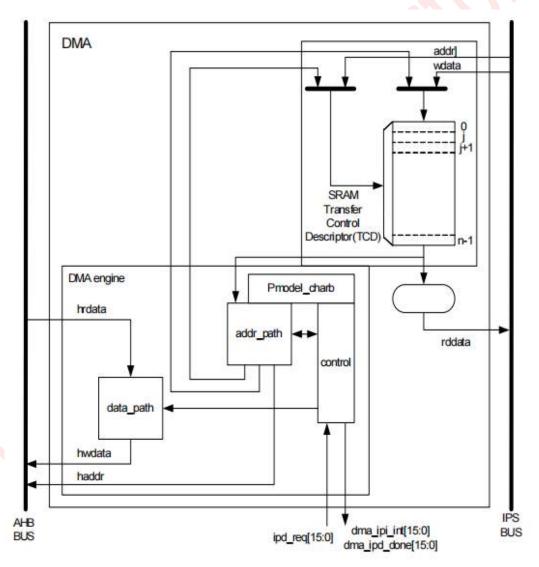

| 13 | . Direct Me  | emory Access (DMA)                  | 154 |

|    | 13.1. Inform | mation Specific to This Device      |     |

|    | 13.1.1.      | Device-Specific Features            | 154 |

|    | 13.1.2.      |                                     |     |

|    | 13.2. Introd | duction                             | 156 |

|    | 13.2.1.      | Features                            | 157 |

| 14 | Option By    | yte (OPB)                           | 158 |

|    | 14.1. Regis  | ster Memory Map                     | 158 |

|    | 14.1.1.      | Register Descriptions               | 158 |

| 15 | . External   | Bus Interface (EBI)                 | 168 |

|    |              | duction                             |     |

|    |              | ures                                |     |

|    | 15.3. Signa  | al Description                      | 168 |

|    |              | ule Memory Map                      |     |

|    |              | ster Descriptions                   |     |

|    | 15.5.1.      | EBI Control Registers 0 (EBICR0)    |     |

|    | 15.5.2.      | EBI Control Registers 1 (EBICR1)    |     |

|    | 15.6. Func   | tional Description                  |     |

|    | 15.6.1.      | EBI_WR#, EBI_RD# Signal Timing      |     |

|    | 15.6.2.      | EBI Functional Description          | 173 |

| 16 | . Programi   | mable Interrupt Timer Modules (PIT) | 175 |

|    | •            | duction                             |     |

|    |              | ς Diagram                           |     |

|    |              | ullet                               | _   |

|     | 16.3. Mode   | es of Operation                           | 175 |

|-----|--------------|-------------------------------------------|-----|

|     | 16.3.1.      | Wait Mode                                 | 175 |

|     | 16.3.2.      | Doze Mode                                 | 175 |

|     | 16.3.3.      | Stop Mode                                 | 175 |

|     | 16.3.4.      | Debug Mode                                | 175 |

|     | 16.4. Signa  | als                                       | 176 |

|     | 16.5. Mem    | nory Map and Registers                    | 176 |

|     | 16.5.1.      | <b>7</b> 1                                |     |

|     | 16.5.2.      | Registers                                 | 176 |

|     | 16.6. Func   | ctional Description                       | 180 |

|     | 16.6.1.      | Set-and-Forget Timer Operation            | 180 |

|     | 16.6.2.      | Free-Running Timer Operation              |     |

|     | 16.6.3.      | Timeout Specifications                    | 181 |

|     | 16.7. Interr | rupt Operation                            | 181 |

| 17. | Watchdo      | og Timer Module (WDT)                     | 182 |

|     | 17.1. Introd | duction                                   | 182 |

|     | 17.2. Mode   | es of Operation                           | 182 |

|     | 17.2.1.      |                                           |     |

|     | 17.2.2.      | Doze Mode                                 |     |

|     | 17.2.3.      | Stop Mode                                 |     |

|     | 17.2.4.      | Debug Mode                                |     |

|     | 17.3. 17.3   | Block Diagram                             | 183 |

|     | 17.4. Signa  | als                                       | 183 |

|     | 17.5. Mem    | nory Map a <mark>nd Registers</mark>      | 183 |

|     |              | Memory Map                                |     |

|     |              | Registers                                 |     |

| 18. | Real Tim     | ne Controller (RTC)                       | 188 |

|     |              | duction                                   |     |

|     |              | ures                                      |     |

|     |              | Mode                                      |     |

|     |              | k Diagram                                 |     |

| 10  |              | ort Module (EPORT)                        |     |

| 13. |              |                                           |     |

|     |              | duction                                   |     |

|     |              | -Power Mode Operation                     |     |

|     | 19.2.1.      | Wait and Doze Modes                       |     |

|     | 19.2.2.      | ·                                         |     |

|     | 19.3. Interi | rupt/General-Purpose I/O Pin Descriptions | 190 |

|     |              |                                           |     |

|    | 19.4. 19.4 N | Memory Map and Registers            | 190 |

|----|--------------|-------------------------------------|-----|

|    | 19.4.1.      | Memory Map                          | 190 |

|    | 19.4.2.      | Registers                           | 190 |

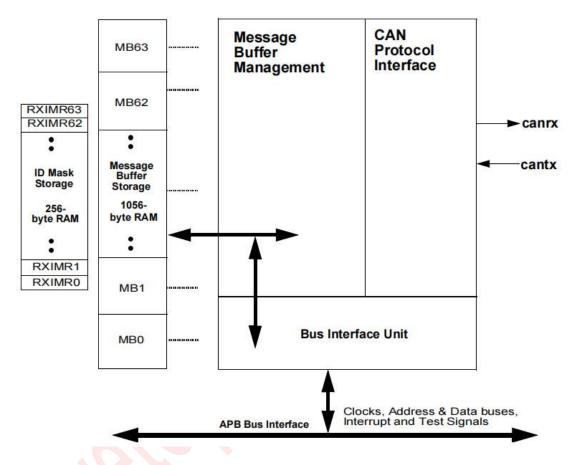

| 20 | . CANBus     | Controller (CANBC)                  | 197 |

|    |              | luction                             |     |

|    | 20.1.1.      | Overview                            | 198 |

|    | 20.1.2.      | CANBus Module Features              | 198 |

|    | 20.1.3.      | Modes of Operation                  | 199 |

|    | 20.2. Exteri | nal Signal Description              | 200 |

|    | 20.2.1.      | Overview                            | 200 |

|    | 20.2.2.      | Signal Descriptions                 | 200 |

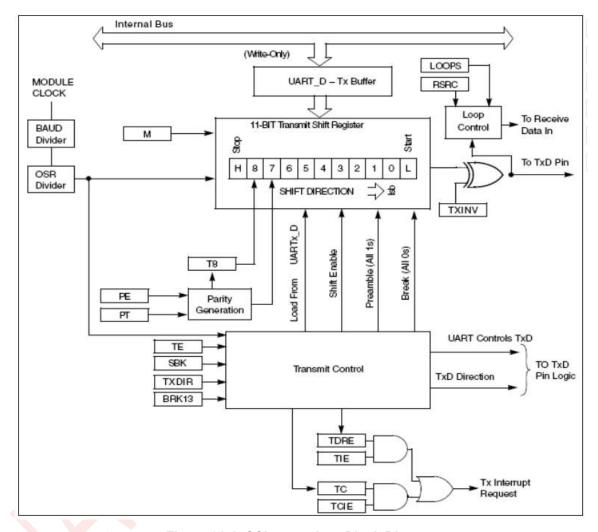

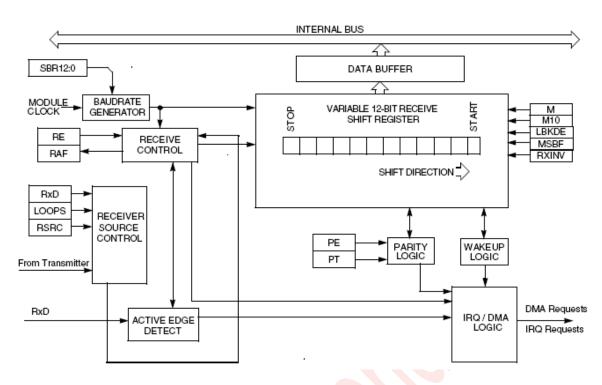

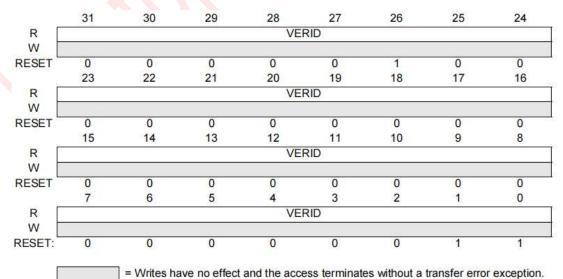

| 21 | . Serial Co  | mmunication Interface Module (SCI)  | 201 |

|    |              | luction                             |     |

|    | 21.2. Featu  | ıres                                | 201 |

|    | 21.3. Mode   | s of Operation                      | 202 |

|    | 21.4. Block  | Diagram                             | 202 |

|    |              | es of Operation                     |     |

|    | 21.5.1.      | Stop Mode                           |     |

|    | 21.5.2.      | Wait Mode                           |     |

|    | 21.6. Signa  | Il Description                      |     |

|    |              | ory Map and Regi <mark>sters</mark> |     |

|    | 21.7.1.      | SCI Version ID Register             | 204 |

|    | 21.7.2.      | SCI Parameter Register              | 205 |

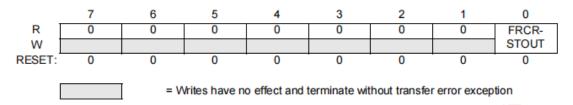

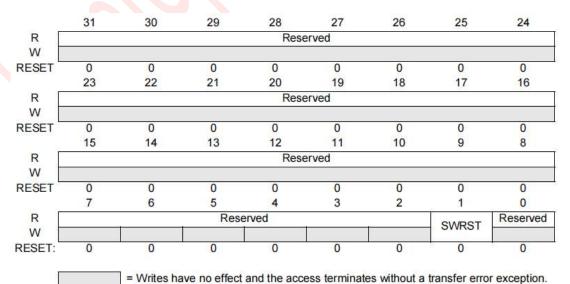

|    | 21.7.3.      | SCI Reset Register                  | 205 |

|    | 21.7.4.      | SCI Pin Register                    | 206 |

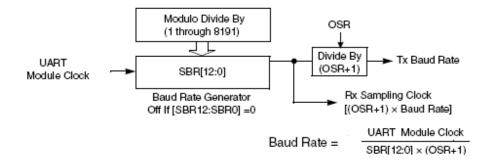

|    | 21.7.5.      | SCI Baud Rate Register              | 207 |

|    | 21.7.6.      | SCI Status Register                 | 209 |

|    | 21.7.7.      | SCI Control Register                | 213 |

|    | 21.7.8.      | SCI Data Register                   |     |

|    | 21.7.9.      | SCI Match Address Register          |     |

|    |              | SCI Modem IrDA Register             |     |

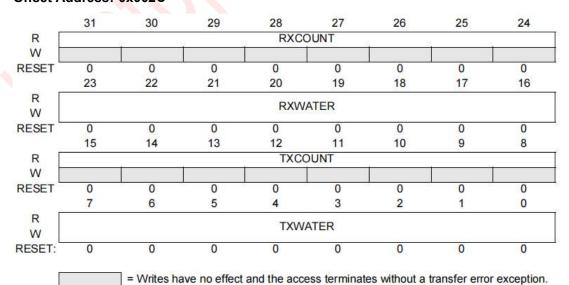

|    |              | SCI FIFO Register                   |     |

|    |              | SCI Watermark Register              |     |

|    |              | SCI Oversampling Ratio Register     |     |

|    |              | ional Description                   |     |

|    |              | Rate Generation                     |     |

|    | 21.10. Trans | mitter Functional Description       | 225 |

|    | 21.10.       | Send Break And Queued Idle                                   | 226 |

|----|--------------|--------------------------------------------------------------|-----|

|    | 21.11. Red   | ceiver Functional Description                                | 227 |

|    | 21.11.       | 1. Data Sampling Technique                                   | 227 |

|    | 21.11.       | 2. Receiver Wakeup Operation                                 | 228 |

|    | 21.11.       | 3. Infrared Decoder                                          | 230 |

|    | 21.12. Add   | litional SCI Functions                                       | 231 |

|    | 21.12.       | 1. 8bit, 9bit and 10bit Data Modes                           | 231 |

|    | 21.12.       | 2. Idle Length                                               | 231 |

|    | 21.12.       | 3. Single-wire Operation                                     | 232 |

|    | 21.12.       | 4. Loop Mode                                                 | 232 |

|    | 21.13. Infra | ared Interface                                               | 232 |

|    | 21.13.       | 1. Infrared Transmit Encoder                                 | 232 |

|    | 21.13.       | 2. Infrared Receive Decoder                                  | 233 |

|    | 21.14. Inte  | rrupts and Status Flags                                      | 233 |

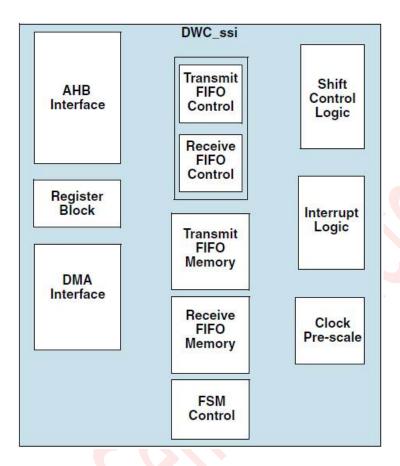

| 22 | . Synchro    | onous Serial Interface (SSI)                                 | 234 |

|    | 22.1. Intro  | oduction                                                     | 234 |

|    | 22.2. Fea    | atures                                                       | 234 |

|    |              | des of Operation                                             |     |

|    |              | ck Diagram                                                   |     |

|    |              | dule Memory Map                                              |     |

|    |              | gister Descriptions                                          |     |

|    | 22.6.1       |                                                              |     |

|    | 22.6.2       |                                                              |     |

|    | 22.6.3       |                                                              |     |

|    | 22.6.4       | . Microwire Control Register(MWCR)                           | 242 |

|    | 22.6.5       | . Slave Enable Register(SER)                                 | 243 |

|    | 22.6.6       |                                                              |     |

|    | 22.6.7       | . Transmit FIFO Threshold Level(TXFTLR)                      | 245 |

|    | 22.6.8       | . Receive FIFO Threshold Level(RXFTLR)                       | 246 |

|    | 22.6.9       | Transmit FIFO Level Register(TXFLR)                          | 247 |

|    | 22.6.1       | 0. Receive FIFO Level Register(RXFLR)                        | 247 |

|    | 22.6.1       | 1. Status Register(SR)                                       | 248 |

|    | 22.6.1       | 2. Interrupt Mask Register(IMR)                              | 249 |

|    | 22.6.1       | Interrupt Status Register(ISR)                               | 250 |

|    | 22.6.1       | 4. Raw Interrupt Status Register(RISR)                       | 251 |

|    | 22.6.1       | 5. Transmit FIFO Overflow Interrupt Clear Registers.(TXOICR) | 252 |

|    | 22.6.1       | 6. Receive FIFO Overflow Interrupt Clear Register(RXOICR)    | 253 |

|    | 22.6.1       | 7. Receive FIFO Underflow Interrupt Clear Register(RXUICR)   | 253 |

|    |              |                                                              |     |

| 22.6.18.      | Interrupt Clear Register(ICR)                               | 254 |

|---------------|-------------------------------------------------------------|-----|

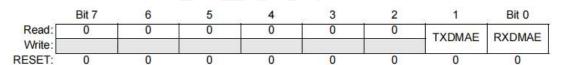

| 22.6.19.      | DMA Control Register(DMACR)                                 | 255 |

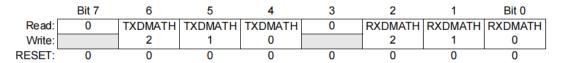

| 22.6.20.      | DMA Transmit Data Level(DMATDLR)                            | 256 |

| 22.6.21.      | DMA Receive Data Level(DMARDLR)                             | 257 |

| 22.6.22.      | Identification Register(IDR)                                | 258 |

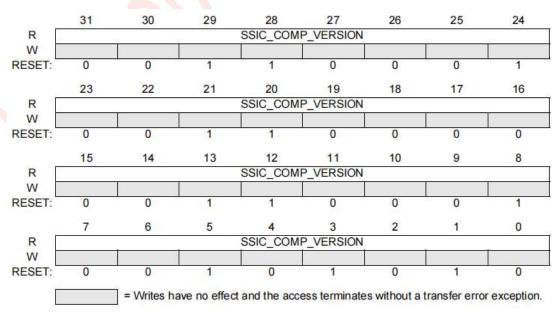

| 22.6.23.      | Version ID Register(VIDR)                                   | 258 |

| 22.6.24.      | SSI Data Register(DRx)                                      | 259 |

|               | RX Sample Delay Register (RXSDR)                            |     |

|               | SPI Control Register 0(SPICTRLR0)                           |     |

| 22.6.27.      | XIP Mode Bits(XIPMBR)                                       | 262 |

| 22.6.28.      | XIP Incr Inst Register(XIPIIR)                              | 263 |

| 22.6.29.      | XIP Wrap Inst Register(XIPWIR)                              | 264 |

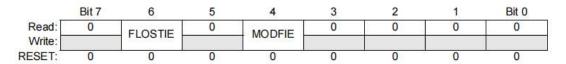

|               | XIP Control Register(XIPCR)                                 |     |

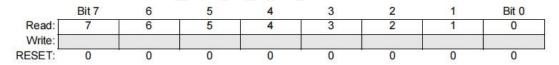

| 22.6.31.      | XIP Slave Enable Register(XIPSER)                           | 267 |

| 22.6.32.      | XIP Receive FIFO Overflow Interrupt Clear Register(XRXIOCR) | 268 |

| 22.6.33.      | XIP Continues Transfer Time Out Register(XIPCTTOR)          | 269 |

| 22.7. Funct   | tional Description                                          | 270 |

| 22.7.1.       | Master Mode                                                 | 270 |

| 22.7.2.       | Clock Ratios                                                | 270 |

| 22.7.3.       | Receive and Transmit FIFO Buffers                           | 271 |

| 22.7.4.       | DMA Operation                                               | 271 |

| 22.7.5.       | SSI Interrupts                                              | 271 |

| 22.7.6.       | Enhanced SPI Modes                                          | 272 |

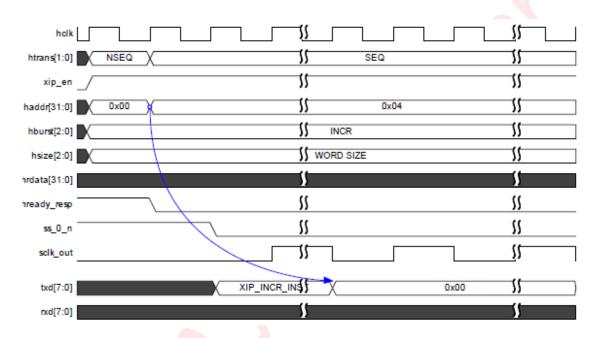

| 22.7.7.       | Execute In Place (XIP) Mode                                 | 273 |

| 22.7.8.       | Continuous Transfer Mode in XIP                             | 273 |

| 22.7.9.       | Data Pre-fetch in XIP Operations                            | 274 |

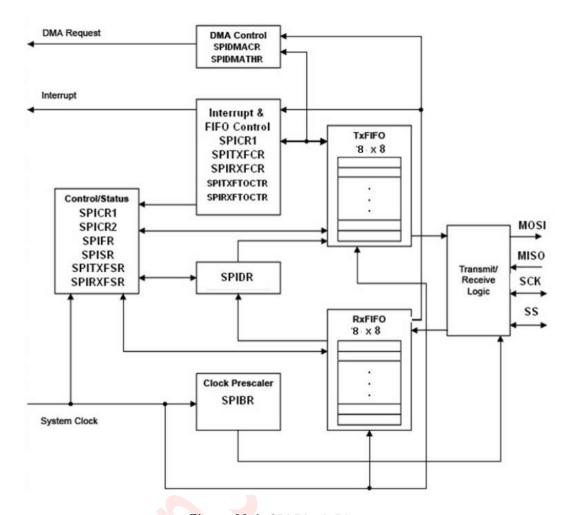

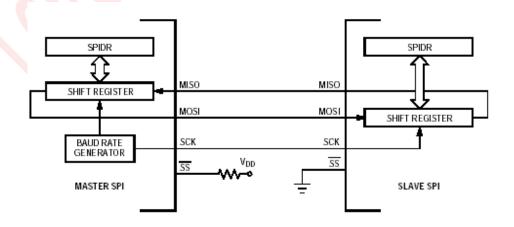

| 23. Serial Pe | ripheral Interface Module (SPI)                             | 275 |

| 23.1. Introd  | duction                                                     | 275 |

| 23.2. Featu   | ıres                                                        | 275 |

|               | es of Operation                                             |     |

|               | Diagram                                                     |     |

|               | al Description                                              |     |

| 23.5.1.       | MISO (Master In/Slave Out)                                  |     |

| 23.5.2.       | MOSI (Master Out/Slave In)                                  |     |

| 23.5.3.       | SCK (Serial Clock)                                          |     |

| 23.5.4.       | SS (Slave Select)                                           |     |

|               | ory Map and Registers                                       |     |

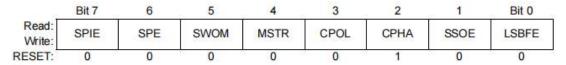

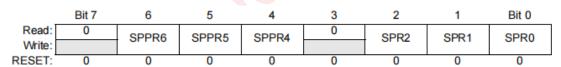

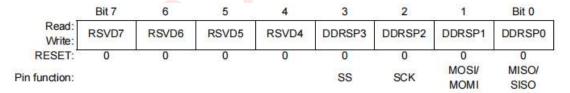

| 23.6.1.       | SPI Control Register                                        |     |

| 20.0.1.       |                                                             |     |

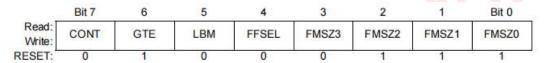

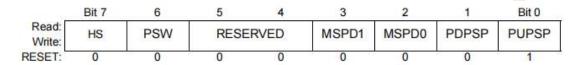

|     | 23.6.2.    | SPI Control Register 2                | .280 |

|-----|------------|---------------------------------------|------|

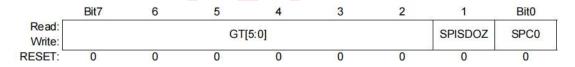

|     | 23.6.3.    | SPI Baud Rate Register                | .281 |

|     | 23.6.4.    | SPI Frame Register                    | .283 |

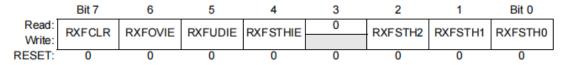

|     | 23.6.5.    | SPI RX FIFO Control Register          | .284 |

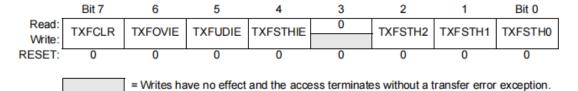

|     | 23.6.6.    | SPI TX FIFO Control Register          | .284 |

|     | 23.6.7.    | SPI RX FIFO TimeOut Counter Register  | .285 |

|     | 23.6.8.    | SPI TX FIFO TimeOut Counter Register  | .286 |

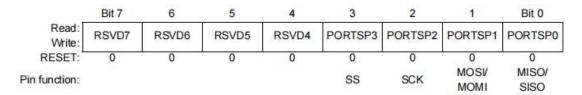

|     | 23.6.9.    | SPI Port Data Direction Register      | .286 |

|     | 23.6.10.   | SPI Pullup and Reduced Drive Register | .287 |

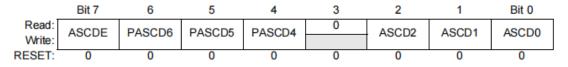

|     | 23.6.11.   | SPI After SCK Delay Register          | .288 |

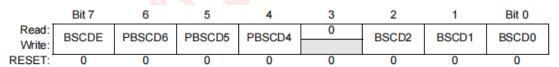

|     | 23.6.12.   | SPI Before SCK Delay Register         | .288 |

|     | 23.6.13.   | SPI Port Data Register                | .289 |

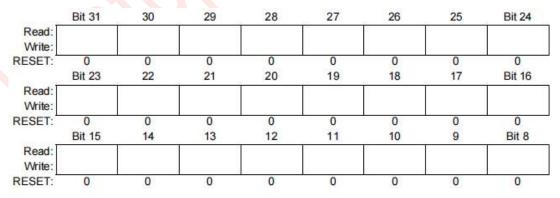

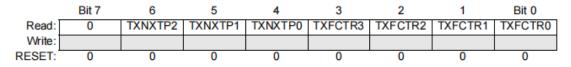

|     | 23.6.14.   | SPI Transmit Counter Register         | .289 |

|     | 23.6.15.   | SPI Data Register                     | .290 |

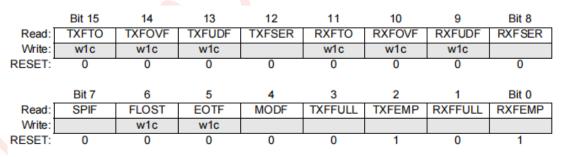

|     | 23.6.16.   | SPI Status Register                   | .290 |

|     | 23.6.17.   | SPI RX FIFO Status Register           | .292 |

|     | 23.6.18.   | SPI TX FIFO Status Register           | .293 |

|     | 23.6.19.   | SPI DMA Control Register              | .293 |

|     |            | SPI DMA Threshold Register            |      |

|     | 23.6.21.   | SPI FIFO Debug Control Register       | .294 |

|     | 23.6.22.   | SPI Interrupt Control Register        | .295 |

|     | 23.6.23.   | SPI RX FIFO Debug Register            | .295 |

|     | 23.6.24.   | SPI TX FIFO Debug Register            | .296 |

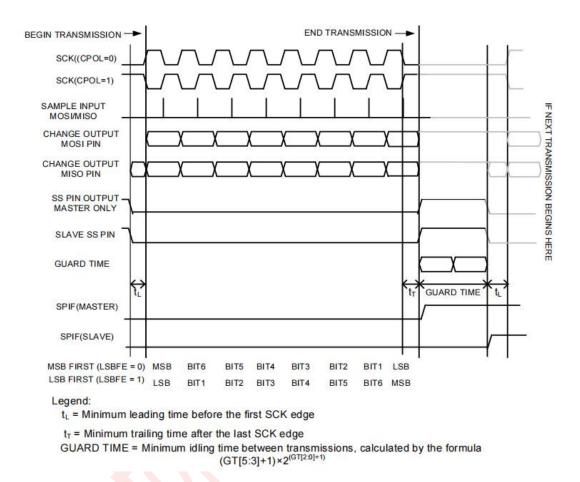

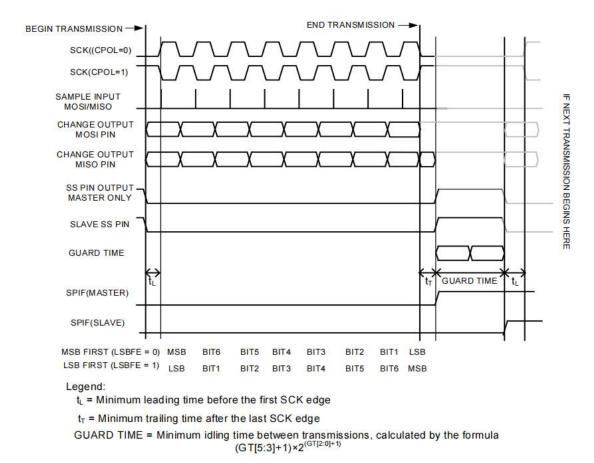

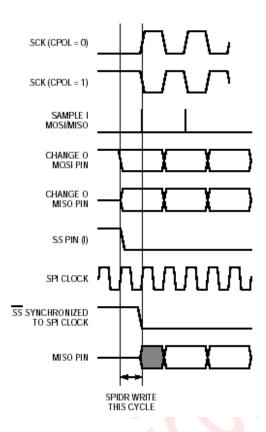

| 23. | 7. Functi  | ional Description                     | 296  |

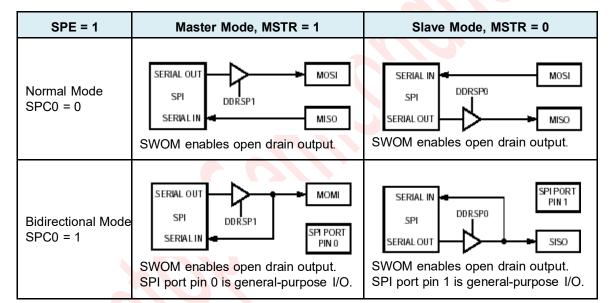

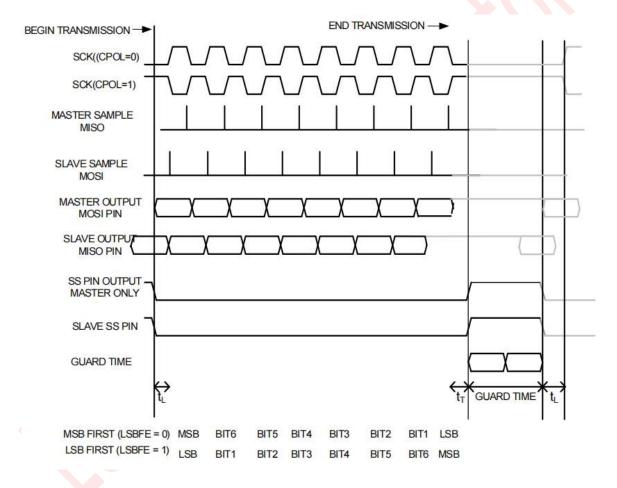

|     | 23.7.1.    | Master Mode                           | .297 |

|     | 23.7.2.    | Slave Mode                            | .297 |

|     | 23.7.3.    | FIFO Operation                        | .298 |

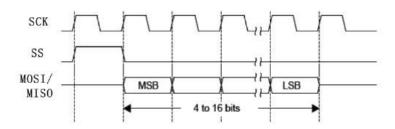

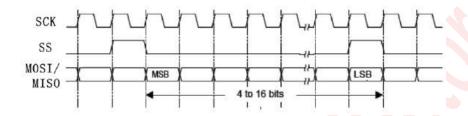

|     | 23.7.4.    | Transmission Formats                  | .298 |

|     | 23.7.5.    | SPI Baud Rate Generation              | .302 |

|     | 23.7.6.    | Slave-Select Output                   | .302 |

|     | 23.7.7.    | Bidirectional Mode                    | .303 |

|     | 23.7.8.    | DMA Operation                         | .303 |

|     | 23.7.9.    | High Speed Mode                       | .304 |

|     | 23.7.10.   | Low-Power Mode Options                | .305 |

| 23. | 8. Reset   | ·                                     | 305  |

| 23. | 9. Interru | ıpts                                  | 306  |

|     | 23.9.1.    | Mode Fault (MODF) Flag                |      |

|     |            | EOT Interrupt Flag (EOTF)             |      |

|     |            |                                       |      |

| 23.9.3.         | Frame Lost Interrupt Flag (FLOST)                     | 306 |

|-----------------|-------------------------------------------------------|-----|

| 23.9.4.         | TXFIFO Timeout Interrupt Flag (TXFTO)                 | 306 |

| 23.9.5.         | TXFIFO Overflow Interrupt Flag (TXFOVF)               | 306 |

| 23.9.6.         | TXFIFO Underflow Interrupt Flag (TXFUDF)              | 307 |

| 23.9.7.         | TXFIFO Service Interrupt Flag (TXFSER)                | 307 |

| 23.9.8.         | RXFIFO Timeout Interrupt Flag (RXFTO)                 | 307 |

| 23.9.9.         | RXFIFO Overflow Interrupt Flag (RXFOVF)               | 307 |

| 23.9.10.        | RXFIFO Underflow Interrupt Flag (RXFUDF)              | 307 |

|                 | RXFIFO Service Interrupt Flag (RXFSER)                |     |

| 24. Inter-Integ | grated Circuit (I2C)                                  | 308 |

| 24.1. Introd    | uction                                                | 308 |

| 24.2. Featu     | res                                                   | 308 |

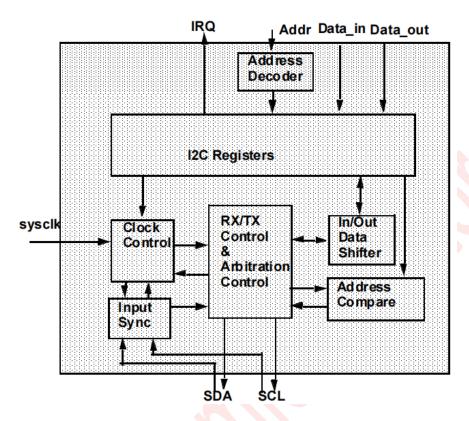

| 24.3. System    | m and Block Diagram                                   | 309 |

|                 | ory Map and Registers                                 |     |

| 24.4.1.         | I2C Status Register(I2CS)                             |     |

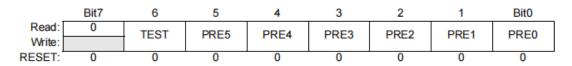

| 24.4.2.         | I2C Clock Prescalar Register (I2CP)                   |     |

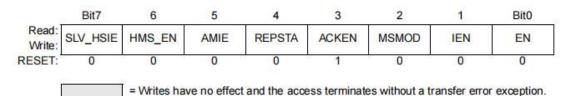

| 24.4.3.         | I2C Control Register (I2CC)                           |     |

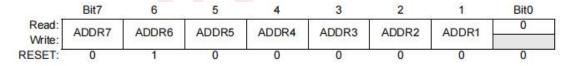

| 24.4.4.         | I2C Slave Address Register (I2CSA)                    |     |

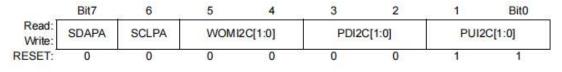

| 24.4.5.         | I2C Port Control Register (I2CPCR)                    | 314 |

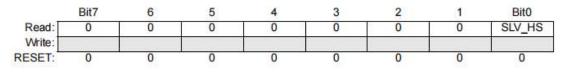

| 24.4.6.         | I2C Slave High-Speed Mode Indicator Register(I2CSHIR) | 315 |

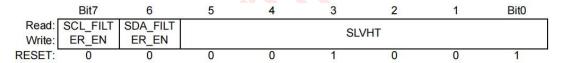

| 24.4.7.         | I2C Slave SDA Hold Time Register(I2CSHT)              | 315 |

| 24.4.8.         | I2C Data Register(I2CD)                               | 316 |

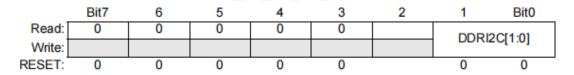

| 24.4.9.         | I2C Port Direction Register (I2CDDR)                  | 316 |

| 24.4.10.        | I2C Port Data Register (I2CPDR)                       | 317 |

| 24.5. Functi    | ional Description                                     | 317 |

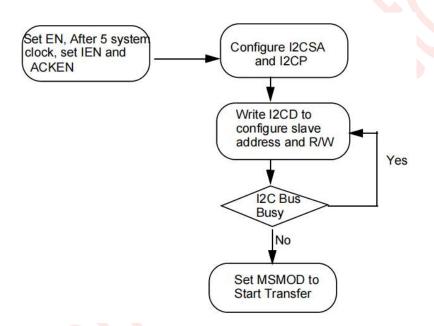

| 24.5.1.         | Master Mode                                           | 317 |

| 24.5.2.         | Slave Mode                                            | 317 |

| 24.5.3.         | Protocol                                              | 318 |

| 24.5.4.         | Arbitration Procedure                                 | 319 |

| 24.5.5.         | Clock Synchronization                                 | 319 |

| 24.5.6.         | Handshaking                                           | 319 |

| 24.5.7.         | Clock Stretching                                      | 319 |

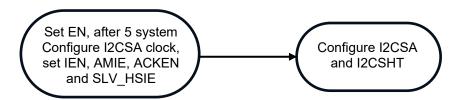

| 24.5.8.         | High-Speed Mode operation                             | 320 |

| 24.5.9.         | Software Transaction Flow Diagrams                    | 322 |

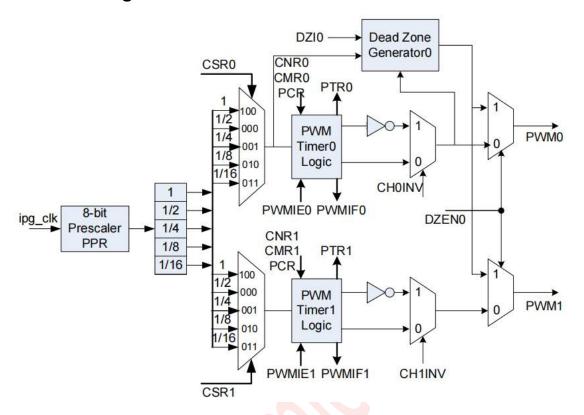

| 25. Pulse Wid   | dth Modulator (PWM)                                   | 325 |

| 25.1. Introd    | uction                                                | 325 |

| 25.2. Featu     | res                                                   | 325 |

|                 | Diagram                                               |     |

|                 | LT165 DS ENG/V1.0A                                    |     |

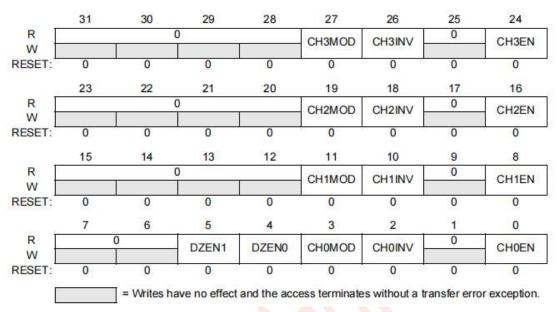

|    | 25.4. Signa  | ll Description                            | 326 |

|----|--------------|-------------------------------------------|-----|

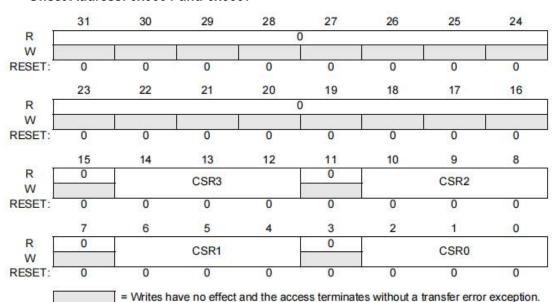

|    | 25.5. Memo   | ory Map and Registers                     | 327 |

|    | 25.5.1.      | Memory Map                                | 327 |

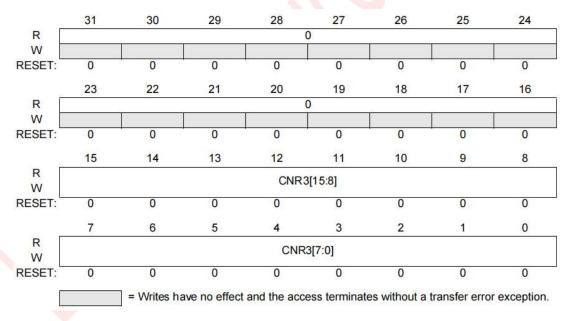

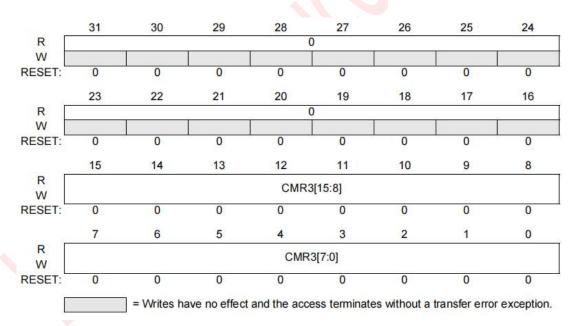

|    | 25.5.2.      | Registers                                 | 328 |

|    | 25.6. Funct  | ional Descriptions                        | 348 |

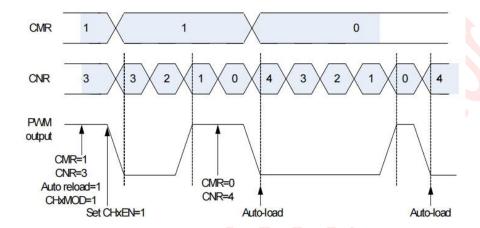

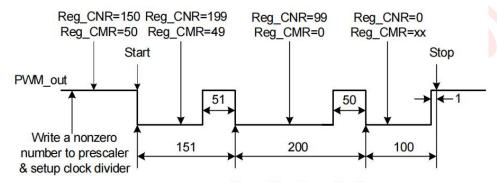

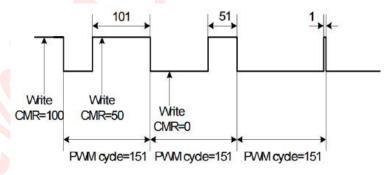

|    | 25.6.1.      | PWM Double Buffering and Automatic Reload | 348 |

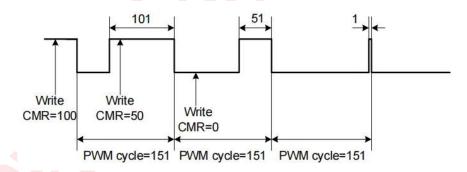

|    | 25.6.2.      | Modulate Duty Ratio                       | 348 |

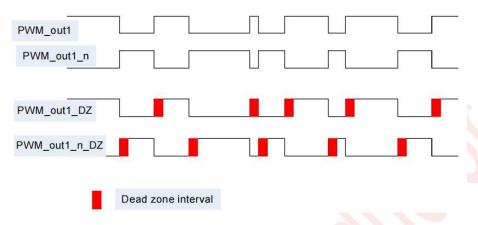

|    | 25.6.3.      | Dead-Zone Generator                       | 349 |

|    | 25.6.4.      | PWM Timer Start Procedure                 | 349 |

|    | 25.6.5.      | PWM Timer Stop Procedure                  | 349 |

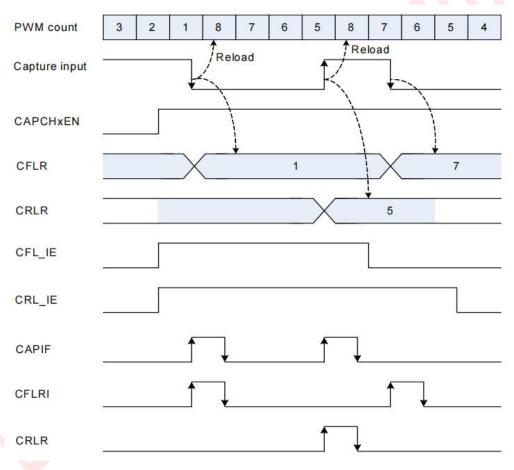

|    | 25.6.6.      | Capture Start Procedure                   | 350 |

|    | 25.6.7.      | Capture Basic Timer Operation             |     |

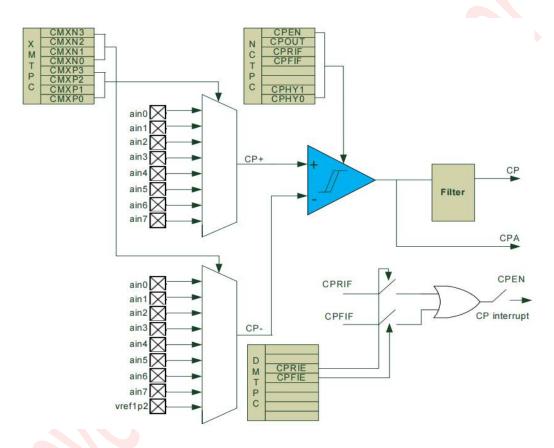

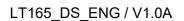

| 26 | . Compara    | tor Modules (COMP)                        | 351 |

|    | 26.1. Introd | luction                                   | 351 |

|    |              | Diagram                                   |     |

|    |              | s of Operation                            |     |

|    | 26.3.1.      | Wait Mode                                 |     |

|    | 26.3.2.      | Doze Mode                                 | 352 |

|    | 26.3.3.      | Stop Mode                                 | 352 |

|    | 26.4. Memo   | ory Map and Regi <mark>s</mark> ters      | 352 |

|    | 26.4.1.      | Memory Map                                | 352 |

|    | 26.4.2.      | Registers                                 | 352 |

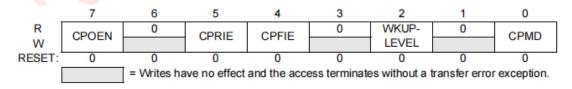

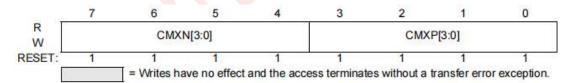

|    | 26.5. Funct  | ion Description                           | 356 |

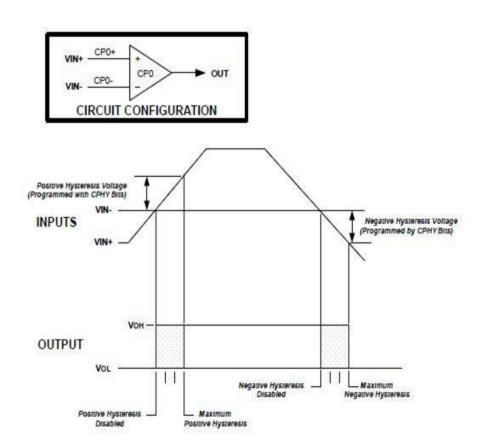

| 27 | . Analog-to  | o-Digital Converter (ADC)                 | 358 |

|    | 27.1. Introd | luction                                   | 358 |

|    |              | Main Features                             |     |

|    |              | Functional Description                    |     |

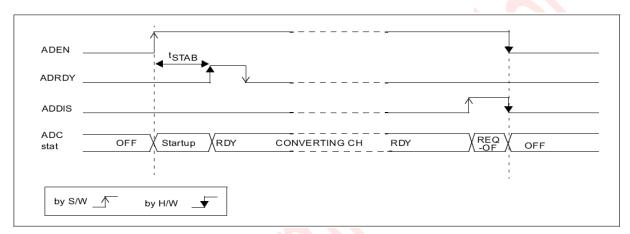

|    | 27.3.1.      | ADC On-Off Control (ADEN, ADDIS, ADRDY)   |     |

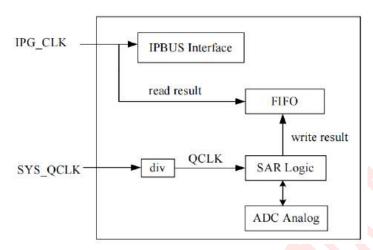

|    | 27.3.2.      | ADC Clock                                 |     |

|    | 27.3.3.      | Configuring the ADC                       | 361 |

|    | 27.3.4.      | Channel Selection (CCWi)                  | 361 |

|    | 27.3.5.      | Programmable Sampling Time (SMP)          |     |

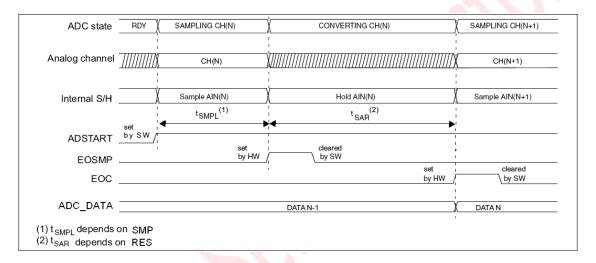

|    | 27.3.6.      | Single Conversion Mode (CONT=0)           | 362 |

|    | 27.3.7.      | Continuous Conversion Mode (CONT=1)       | 363 |

|    | 27.3.8.      | Starting Conversions (ADSTART)            | 363 |

|    | 27.3.9.      | Timings                                   | 364 |

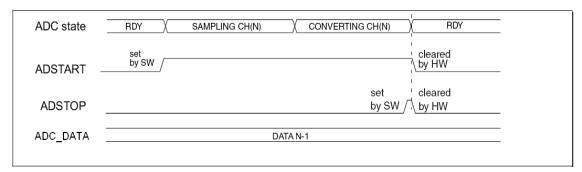

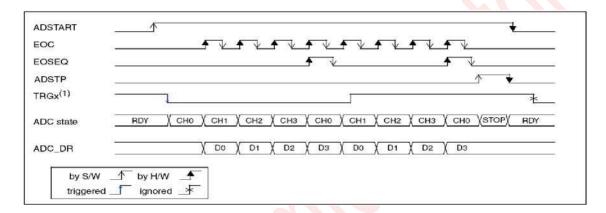

|    | 27.3.10.     | Stopping an Ongoing Conversion (ADSTP)    | 364 |

|    |              |                                           |     |

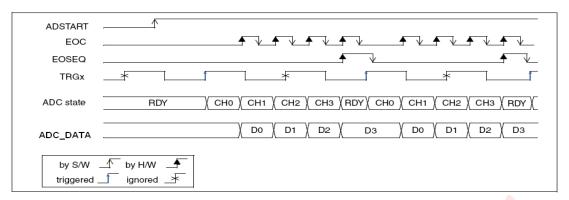

|     | 27.4. Conv   | ersion on External Trigger and Trigger Polarity (TRIGMODE, TRIGSCR)            | 365 |

|-----|--------------|--------------------------------------------------------------------------------|-----|

|     | 27.4.1.      | Discontinuous Mode (DISCEN)                                                    | 366 |

|     | 27.4.2.      | Programmable Resolution (RES) - Fast Conversion Mode                           | 366 |

|     | 27.4.3.      | End of Conversion, End Of Sampling Phase (EOC, EOSMP Flags)                    | 367 |

|     | 27.4.4.      | End of Conversion Sequence (EOSEQ Flag)                                        | 367 |

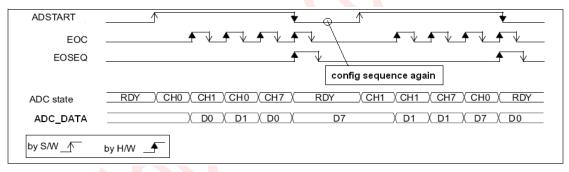

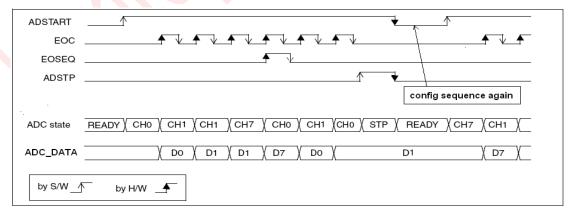

|     | 27.4.5.      | Example Timing Diagrams (Single/Continuous Modes Hardware / Software Triggers) | 367 |

|     | 27.5. Data   | Management                                                                     |     |

|     | 27.5.1.      | Data FIFO & Data Alignment (ADC_FIFO, ALIGN)                                   | 368 |

|     | 27.5.2.      | ADC Overrun (OVR, OVRMOD)                                                      | 369 |

|     | 27.5.3.      | Managing a Sequence of Data Converted Without Using The DMA                    | 369 |

|     | 27.5.4.      | Managing Converted Data Without Using The DMA Without Overrun                  | 369 |

|     | 27.5.5.      | Managing Converted Data Using The DMA                                          | 370 |

|     | 27.6. Low p  | power Features                                                                 | 370 |

|     | 27.6.1.      | Wait Mode Conversion                                                           | 370 |

|     | 27.6.2.      | Auto-off Mode (AUTOFF)                                                         | 370 |

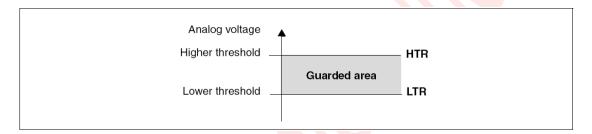

|     |              | og Window Watchdog                                                             |     |

|     |              | perature Sensor                                                                |     |

|     |              | Interrupts                                                                     |     |

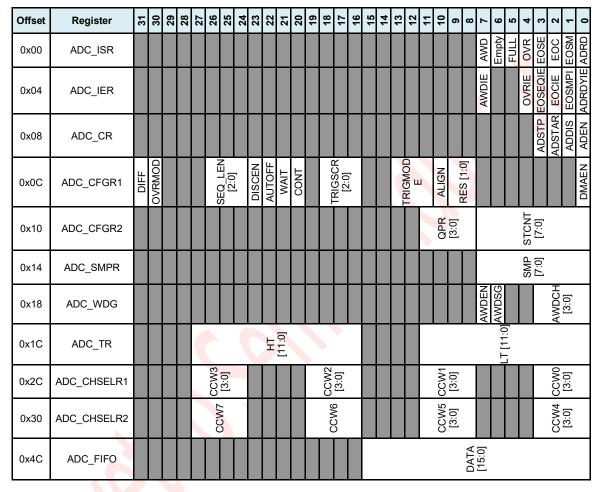

|     | 27.10. Mem   | ory Map and Registers                                                          | 373 |

|     |              | Memory Map                                                                     |     |

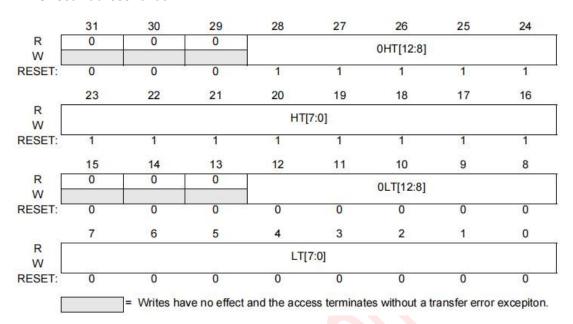

|     | 27.10.2.     | Registers                                                                      | 374 |

| 28  | . Electrical | Characteristic                                                                 | 387 |

|     | 28.1. Abso   | lute Maxim <mark>um Ratings</mark>                                             | 387 |

|     | 28.2. DC E   | lectrical Specification                                                        | 387 |

|     | 28.3. E Ele  | ctrostatic Discharge (ESD) Protection                                          | 388 |

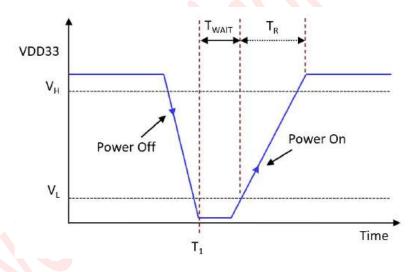

|     | 28.4. VDD    | Power Up Timin                                                                 | 389 |

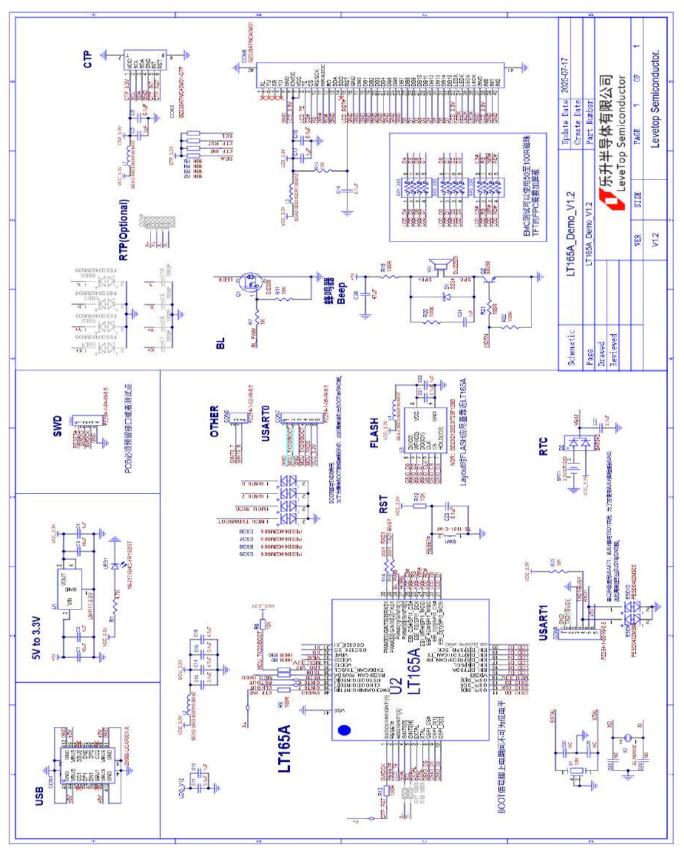

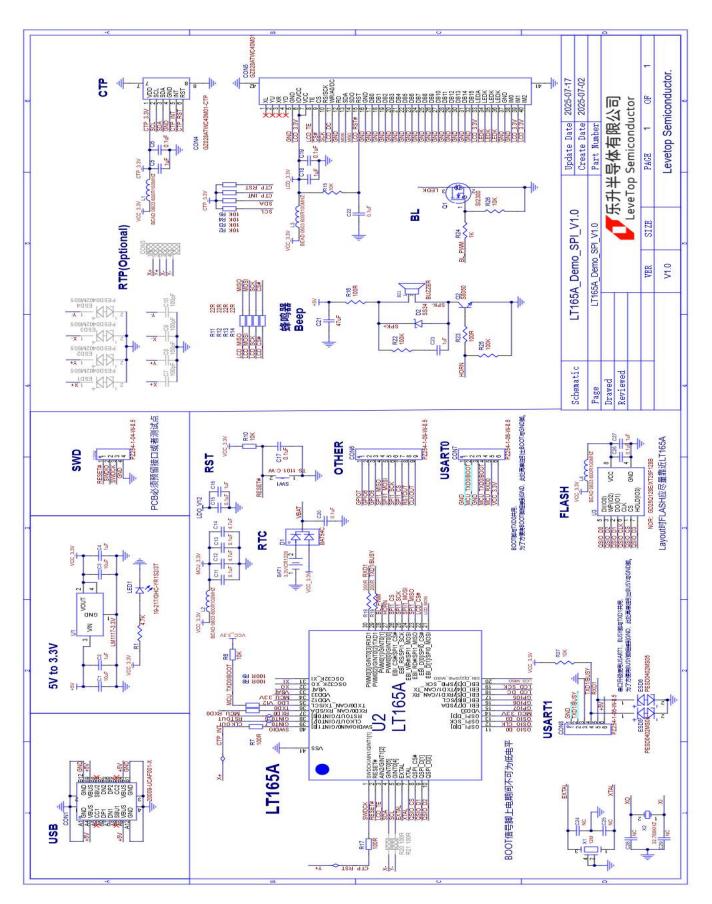

| 29  |              | on Circuit                                                                     |     |

|     |              |                                                                                |     |

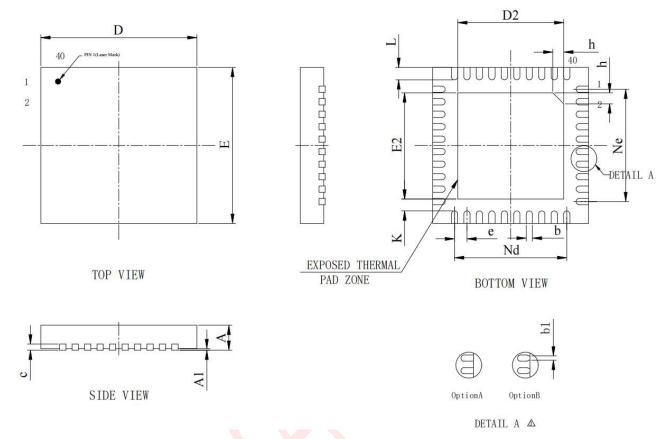

| - • |              | 5A (QFN-40pin)                                                                 |     |

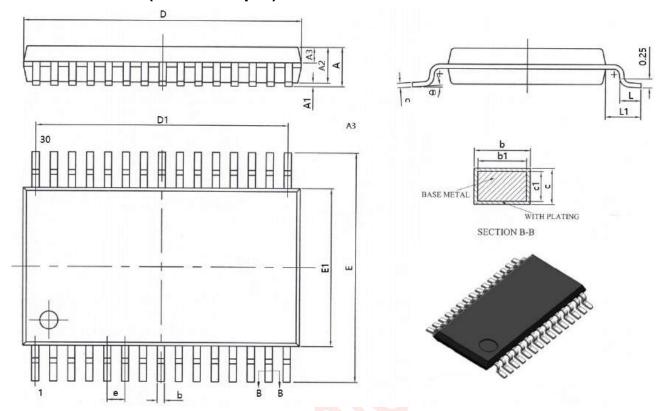

|     |              | 5B (TSSOP-30pin)                                                               |     |

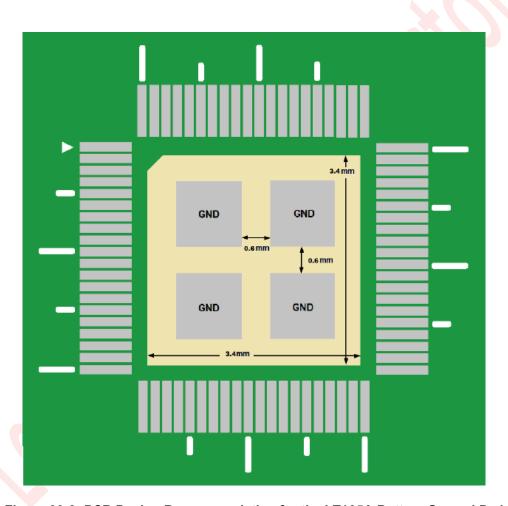

|     |              | Design for Ground Pad                                                          |     |

|     |              |                                                                                |     |

## Figure List

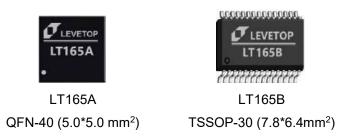

| Figure 1-1: LT165 Package Overview                                   | 28 |

|----------------------------------------------------------------------|----|

| Figure 1-2: Internal Block Diagram                                   | 28 |

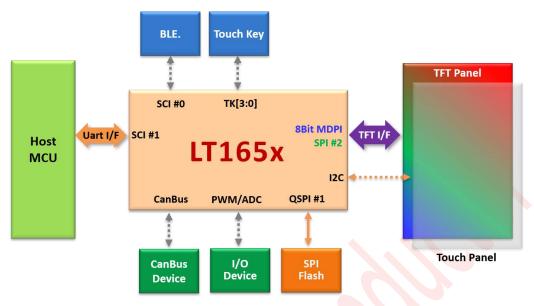

| Figure 1-3: System Block of LT165                                    | 35 |

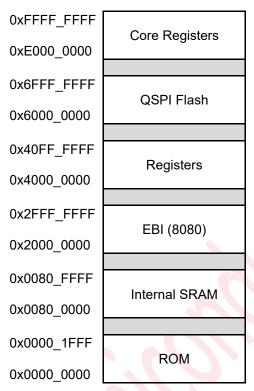

| Figure 1-4: Memory Address Map                                       | 36 |

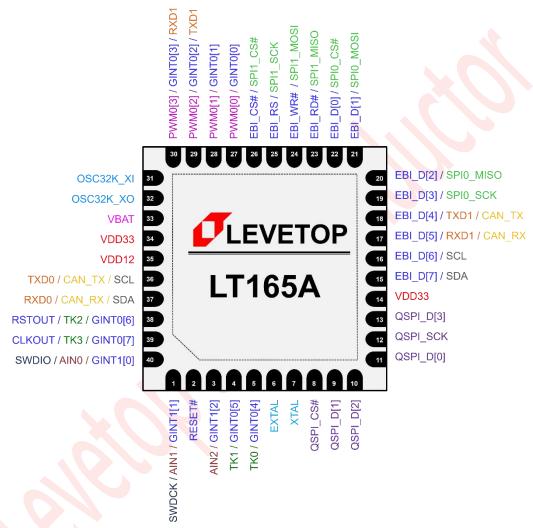

| Figure 2-1: LT165A (QFN-40) Pin Assignment                           | 38 |

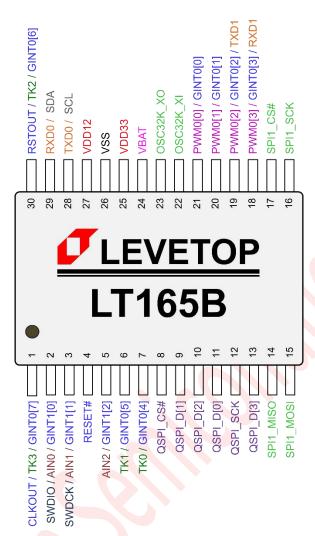

| Figure 2-2: LT165B (TSSOP-30) Pin Assignment                         | 39 |

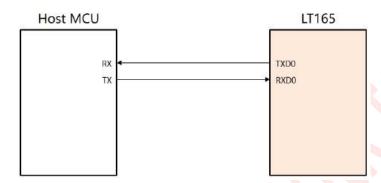

| Figure 3-1: UART Connection Between LT165 and Host MCU               | 50 |

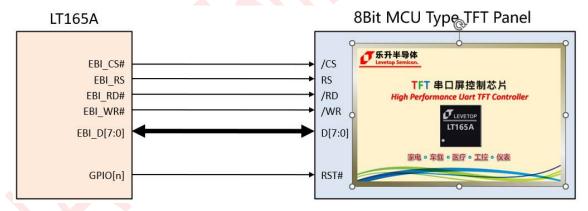

| Figure 3-2: LT165A Connect to 8bits 8080 I/F of TFT LCD Panel        | 50 |

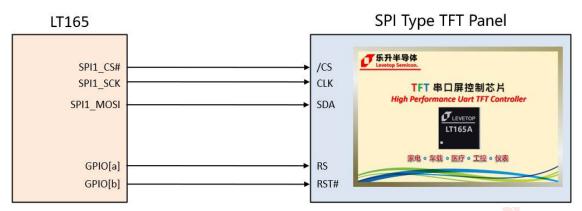

| Figure 3-3: LT165 Connect to SPI I/F of TFT LCD Panel                | 51 |

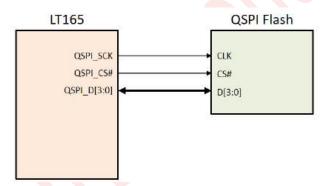

| Figure 3-4: LT165 Connect to QSPI Flash                              | 51 |

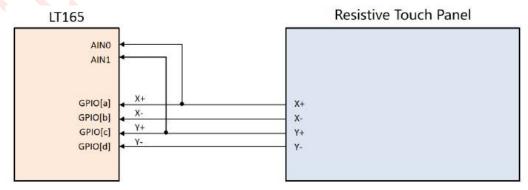

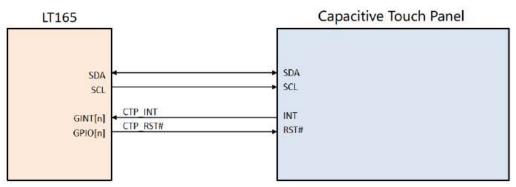

| Figure 3-5: LT165 Connect to Resistive Touch Panel                   |    |

| Figure 3-6: LT165 Connect to Capacitive Touch Panel                  | 52 |

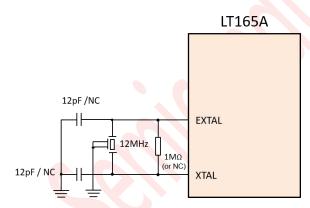

| Figure 3-7: External 12MHz Clock Circuit                             |    |

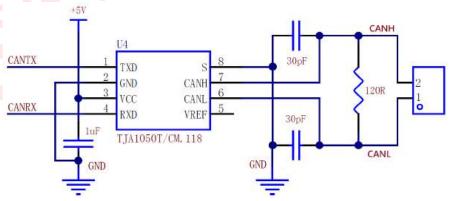

| Figure 3-8: Canbus Circuit Example                                   | 52 |

| Figure 3-9: TFT LCD Backlight Circuit Example 1                      | 53 |

| Figure 3-10: TFT LCD Backlight Circuit Example 2                     | 53 |

| Figure 3-11: RTC Application Circuit                                 |    |

| Figure 3-12: External Reset Circuit                                  | 54 |

| Figure 4-1: Interrupt Control Status Register (ICSR)                 | 57 |

| Figure 4-2: Interrupt Enable Register (IER)                          | 58 |

| Figure 4-3: Interrupt Pend Set Register (IPSR)                       | 59 |

| Figure 4-4: Interrupt Pend Clear Register (IPCR)                     | 60 |

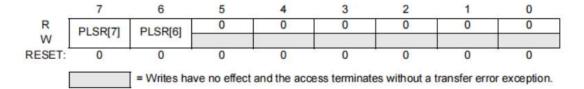

| Figure 4-5: Priority Level Select Registers (PLSR0 ~ PLSR31)         | 61 |

| Figure 4-6: System Priority Level Select Registers (SYSPLSR)         | 62 |

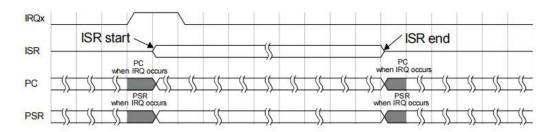

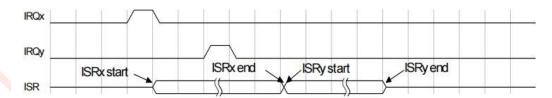

| Figure 4-7: One Pulse Interrupt Without Confliction                  | 63 |

| Figure 4-8: Level-Sensitive Interrupt Without Confliction            | 64 |

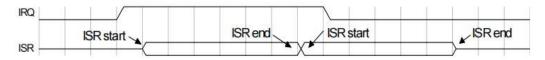

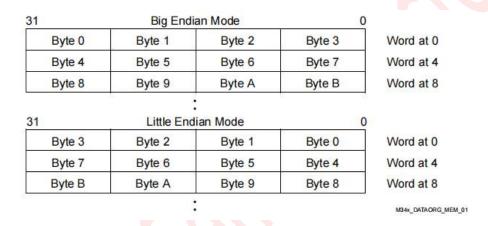

| Figure 4-9: Two Interrupts Occur at The Same Time                    | 64 |

| Figure 4-10: A Lower Priority Interrupt Asserted With Confliction    | 64 |

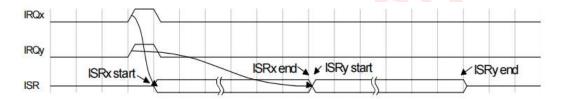

| Figure 4-11: A higher Priority Interrupt Asserted With Confliction   | 64 |

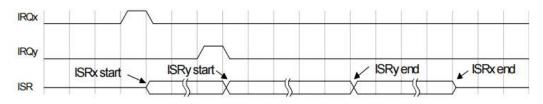

| Figure 5-1: Programming Model                                        | 70 |

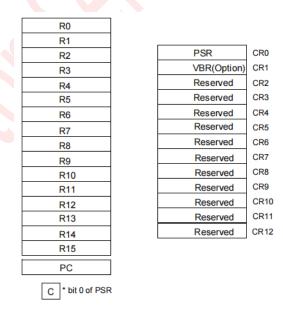

| Figure 5-2: Data Organization in Memory                              | 71 |

| Figure 6-1: EPT Control Status Register (EPTCSR)                     | 76 |

| Figure 6-2: EPT Reload Register (EPTRLD)                             | 77 |

| Figure 6-3: EPT Counter Register (EPTCNT)                            | 78 |

| Figure 6-4: EPT Count Timing                                         | 79 |

| Figure 7-1: SIM Block Diagram                                        | 80 |

| Figure 7-2: Sample PCR Map                                           | 82 |

| Figure 7-3: GPIO Pin Data Out Register 0 ~ 3 (SIM_GPDO0 ~ SIM_GPDO3) | 86 |

| Figure 7-4: GPIO Pin Data Out Register 4 ~ 7 (SIM_GPDO4 ~ SIM_GPDO7) | 87 |

| Figure 7-5: GPIO Pin Data Out Register 8 ~ 11 (SIM_GPDO8 ~ SIM_GPDO11)     | 87  |

|----------------------------------------------------------------------------|-----|

| Figure 7-6: GPIO Pin Data Out Register 12 ~ 15 (SIM_GPDO12 ~ SIM_GPDO15)   | 88  |

| Figure 7-7: GPIO Pin Data Out Register 16 ~ 19 (SIM_GPDO16 ~ SIM_GPDO19)   | 88  |

| Figure 7-8: GPIO Pin Data Out Register 20 ~ 23 (SIM_GPDO20 ~ SIM_GPDO23)   | 89  |

| Figure 7-9: GPIO Pin Data Out Register 24 ~ 27 (SIM_GPDO24 ~ SIM_GPDO27)   | 89  |

| Figure 7-10: GPIO Pin Data Out Register 28 ~ 31 (SIM_GPDO28 ~ SIM_GPDO31)  | 90  |

| Figure 7-11: GPIO Pin Data in Register 0 ~ 3 (SIM_GPDI0 ~ SIM_GPDI3)       | 91  |

| Figure 7-12: GPIO Pin Data in Register 4 ~ 7 (SIM_GPDI4 ~ SIM_GPDI7)       | 91  |

| Figure 7-13: GPIO Pin Data in Register 8 ~ 11 (SIM_GPDI8 ~ SIM_GPDI11)     | 92  |

| Figure 7-14: GPIO Pin Data in Register 12 ~ 15 (SIM_GPDI12 ~ SIM_GPDI15)   | 92  |

| Figure 7-15: GPIO Pin Data in Register 16 ~ 19 (SIM_GPDI16 ~ SIM_GPDI19)   | 93  |

| Figure 7-16: GPIO Pin Data in Register 20 ~ 23 (SIM_GPDI20 ~ SIM_GPDI23)   | 93  |

| Figure 7-17: GPIO Pin Data in Register 24 ~ 27 (SIM_GPDI24 ~ SIM_GPDI27)   | 94  |

| Figure 7-18: GPIO Pin Data in Register 28 ~ 31 (SIM_GPDI28 ~ SIM_GPDI31)   | 94  |

| Figure 7-19: Parallel GPIO Pin Data Output Register (SIM_PGPDO0)           | 95  |

| Figure 7-20: Parallel GPIO Pin Data Input Register(SIM_PGPDI0)             | 96  |

| Figure 7-21: Masked Parallel GPIO Pin Data Output Register (SIM_MPGPDO0)   | 97  |

| Figure 7-22: Masked Parallel GPIO Pin Data Output Register (SIM_MPGPDO1)   | 98  |

| Figure 7-23: WKUPC — Wakeup Configuration Register                         | 99  |

| Figure 7-24: QSPIXIPMCFR — QSPI XIP Mode Configuration Register            | 101 |

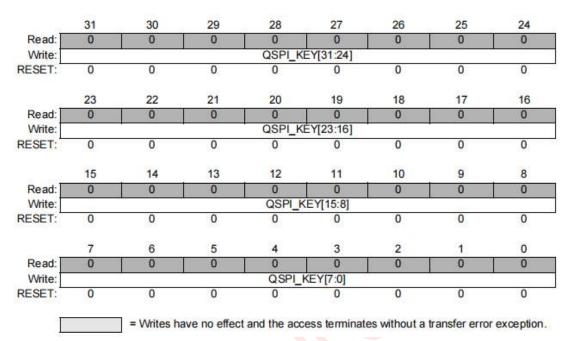

| Figure 7-25: QSPIKEYR — QSPI 32bit Key Register                            | 102 |

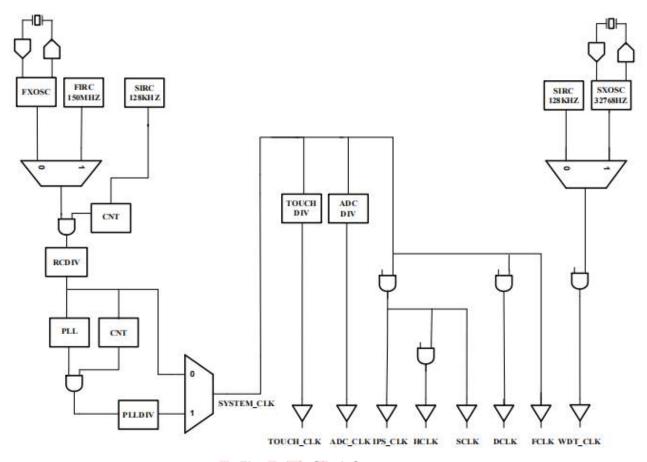

| Figure 8-1: Clock Structure                                                | 104 |

| Figure 8-2: Synthesizer Control Register (SYNCR)                           | 106 |

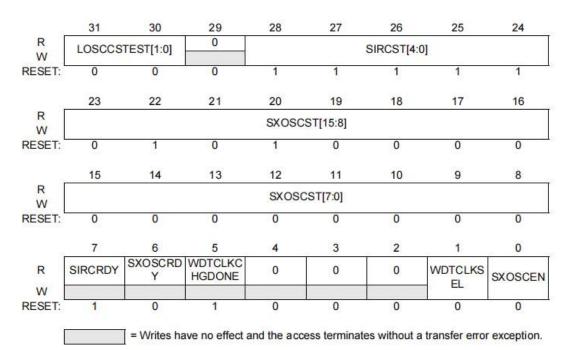

| Figure 8-3: Low Speed Oscillator Control and Status Register (LOSCCSR)     | 110 |

| Figure 8-4: PLL Configuration and Status Register (PLLCSR)                 | 111 |

| Figure 8-5: Module Stop Control Register (MSCR)                            | 113 |

| Figure 8-6: EPT External and CLKOUT Clock Source Control Register (ECCSCR) | 115 |

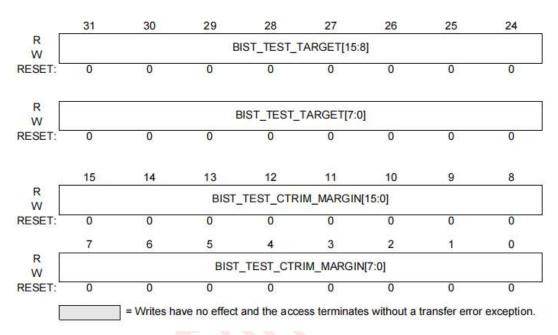

| Figure 8-7: OSC Bist Test Configuration Register1(OBTCR1)                  | 116 |

| Figure 8-8: OSC Bist Test Configuration Register2(OBTCR2)                  | 117 |

| Figure 8-9: OSC Bist Test Control Register(OBTCR)                          | 118 |

| Figure 8-10: OSC BIST Test Counter Register(OBTCNTR)                       | 119 |

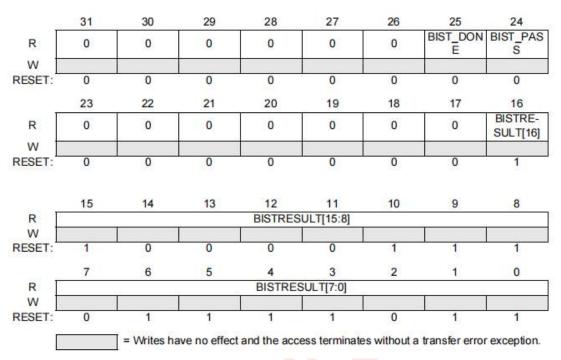

| Figure 8-11: OSC BIST Test Result Register(OBTRR)                          | 120 |

| Figure 9-1: Reset Controller Block Diagram                                 | 123 |

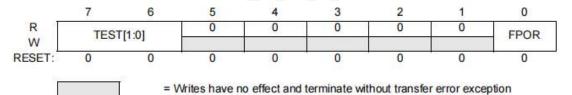

| Figure 9-2: Reset Test Register(RTR)                                       | 124 |

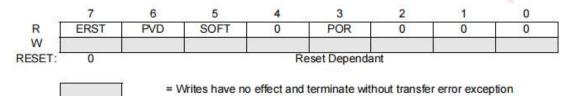

| Figure 9-3: Reset Status Register(RSR)                                     | 125 |

| Figure 9-4: Reset Control Register(RCR)                                    | 126 |

| Figure 9-5: Reset Control Flow                                             | 128 |

| Figure 11-1: Cache Module Block Diagram                                    | 131 |

| Figure 11-2: Cache Control Register (LMEM_CCR)                             | 132 |

| Figure 11-3: Cache Line Control Register (LMEM_CLCR)                       | 133 |

| Figure 11-4: Cache Search Address Register (LMEM_CSAR)                     | 135 |

| Figure 11-5: Cache Search Address Register (LMEM_CSAR)                                              | 136    |

|-----------------------------------------------------------------------------------------------------|--------|

| Figure 11-6: Cache Access Register(LMEM_ACRG)                                                       | 137    |

| Figure 11-7: Cache Page Invalidate Base Address Register (LMEM_PAGE_INV_BADDR)                      | 138    |

| Figure 11-8: Cache Page Invalidate Size Register (LMEM_PAGE_INV_SIZE)                               | 139    |

| Figure 11-9: Cache Clock Enable Register (LMEM_CACHE_CLK_EN)                                        | 140    |

| Figure 11-10: Cache Tag and Data Access Structure                                                   | 141    |

| Figure 11-11: Cache Set Commands                                                                    | 142    |

| Figure 11-12: Cache Line Commands                                                                   | 143    |

| Figure 11-13: Line Command Results                                                                  | 144    |

| Figure 12-1: XBAR Device-Specific Block Diagram                                                     |        |

| Figure 12-2: Master Priority Register (XBAR_MPRn)                                                   | 147    |

| Figure 12-3: Slave General Purpose Control Register (XBAR_SGPCRn)                                   | 149    |

| Figure 13-1: DMA Block Diagram                                                                      | 156    |

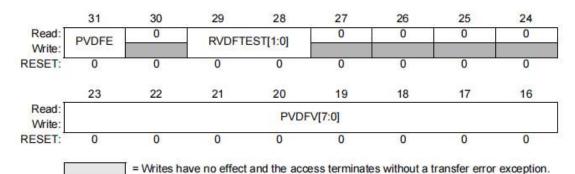

| Figure 14-1: PVDC — Programmable Voltage Detector Configuration Register                            |        |

| Figure 14-2: CCR — Customer Configuration Register                                                  | 160    |

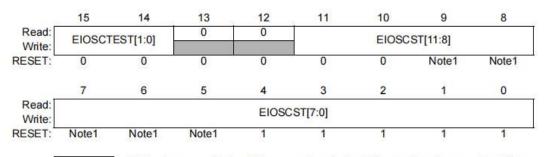

| Figure 14-3: EIOSCST — External or Internal High Speed Oscillator Stable Time Configuration Registe | r .161 |

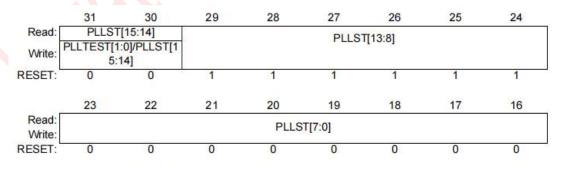

| Figure 14-4: PLLOCKCR — PLL Lock Time Configuration Register                                        | 161    |

| Figure 14-5: RFEVR — RESET pin Filter Enable and Value Register                                     | 162    |

| Figure 14-6: PVDFEVR — Programmable Voltage Detector Filter Enable and Value Register               | 163    |

| Figure 14-7: IOSCTC — Internal High Speed Oscillator Trimming Configuration Register                | 164    |

| Figure 14-8: VREFTCR — VREF Trimming Configuration Register                                         | 165    |

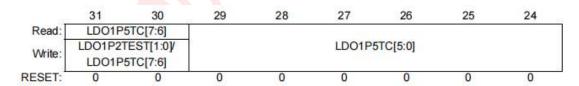

| Figure 14-9: LDO1P5TC — LDO1P2 Trimming Configuration Register                                      | 165    |

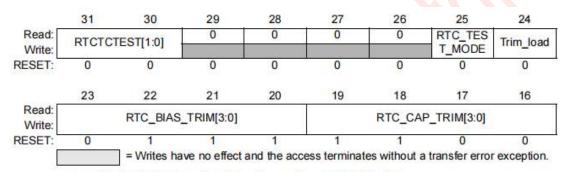

| Figure 14-10: RTCTCR — RTC Trimming Configuration Register                                          | 166    |

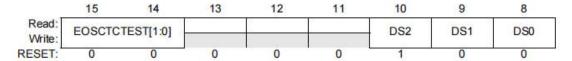

| Figure 14-11: EOSCTCR — External Oscillator Trimming Configuration Register                         | 167    |

| Figure 15-1: EBI Control Regis <mark>ter 0 (EBICR0).</mark>                                         |        |

| Figure 15-2: EBI Control Register 1 (EBICR1)                                                        | 171    |

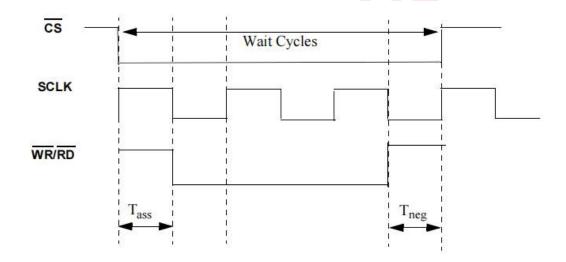

| Figure 15-3: EBI_WR#, EBI_RD# Assert/Negate Timing                                                  | 172    |

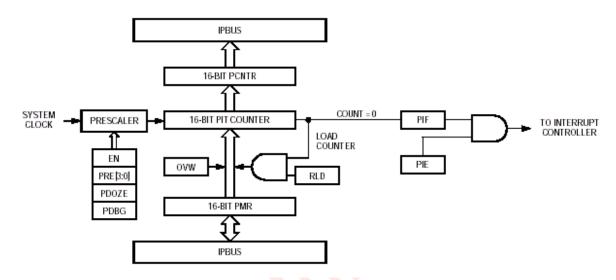

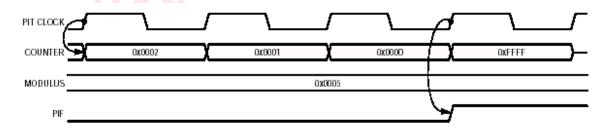

| Figure 16-1: PIT Block Diagram                                                                      | 175    |

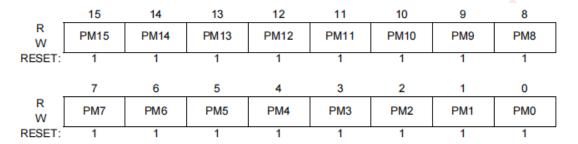

| Figure 16-2: PIT Modulus Register (PMR)                                                             | 177    |

| Figure 16-3: PIT Control and Status Register (PCSR)                                                 | 177    |

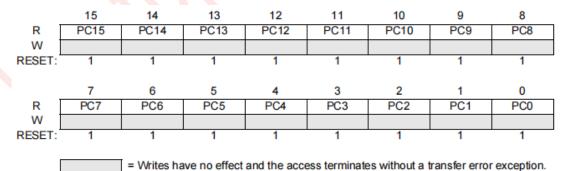

| Figure 16-4: PIT Count Register (PCNTR)                                                             | 179    |

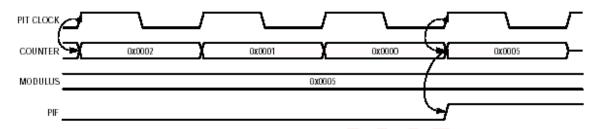

| Figure 16-5: Counter Reloading from the Modulus latch                                               | 180    |

| Figure 16-6: Counter in Free-Running Mode                                                           | 180    |

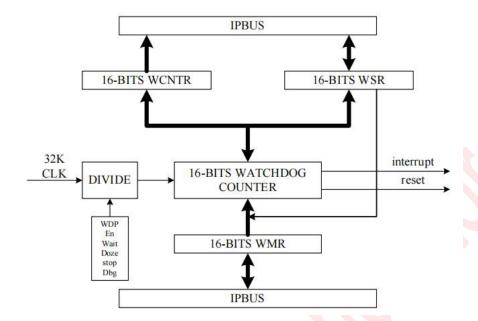

| Figure 17-1: Watchdog Timer Block Diagram                                                           | 183    |

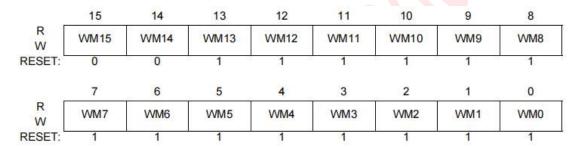

| Figure 17-2: Watchdog Modulus Register (WMR)                                                        | 184    |

| Figure 17-3: Watchdog Control Register (WCR)                                                        | 185    |

| Figure 17-4: Watchdog Service Register (WSR)                                                        | 187    |

| Figure 17-5: Watchdog Count Register (WCNTR)                                                        | 187    |

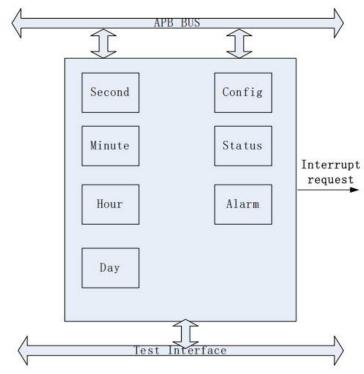

| Figure 18-1: RTC Block Diagram                                                                      | 188    |

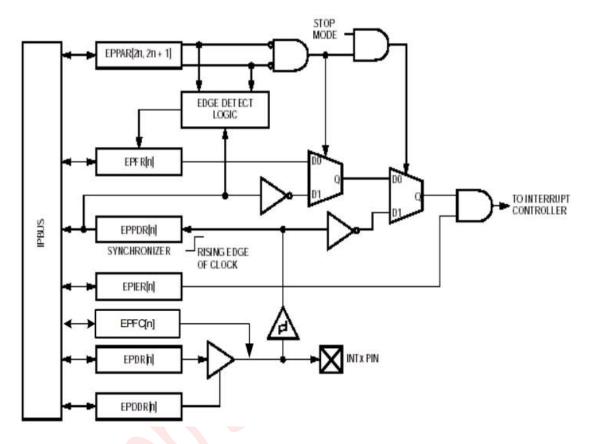

| Figure 19-1: EPORT Block Diagram                                                                    | 189    |

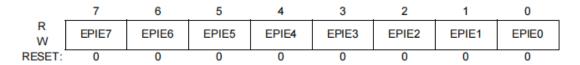

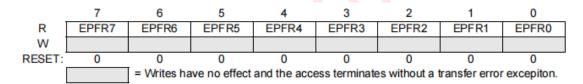

| Figure 19-2: EPORT Port Interrupt Enable Register (EPIER)                                           | 191    |

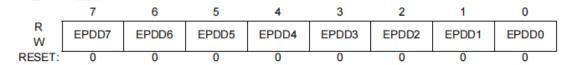

| Figure 19-3: EPORT Data Direction Register (EPDDR)         | 191 |

|------------------------------------------------------------|-----|

| Figure 19-4: EPORT Pin Assignment Register (EPPAR)         | 192 |

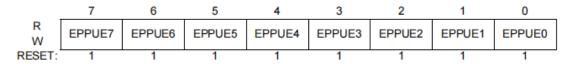

| Figure 19-5: EPORT Pin Pull-up Enable Register (EPPUE)     | 193 |

| Figure 19-6: EPORT Port Flag Register (EPFR)               | 193 |

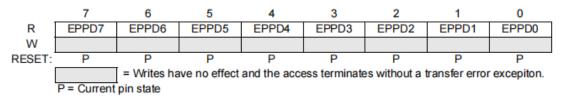

| Figure 19-7: EPORT Port Pin Data Register (EPPDR)          | 194 |

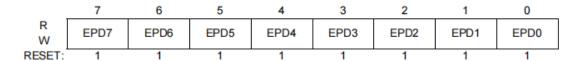

| Figure 19-8: EPORT Port Data Register (EPDR)               | 194 |

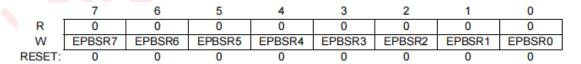

| Figure 19-9: EPORT Port Bit Set Register (EPBSR)           | 194 |

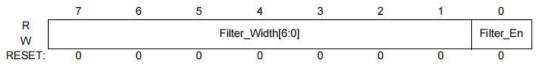

| Figure 19-10: EPORT Digital Filter Control Register (EPFC) | 195 |

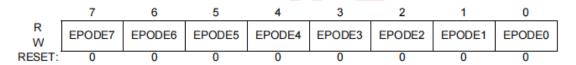

| Figure 19-11: EPORT Open Drain Enable Register (EPODE)     | 195 |

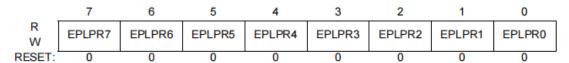

| Figure 19-12: EPORT Level Polarity Register (EPLPR)        | 196 |

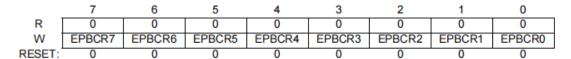

| Figure 19-13: EPORT Port Bit Clear Register (EPBCR)        | 196 |

| Figure 20-1: CANBus Block Diagram                          | 197 |

| Figure 21-1: SCI transmitter Block Diagram                 |     |

| Figure 21-2: SCI Receiver Block Diagram                    | 203 |

| Figure 21-3: SCI Version ID Register(SCI_VERID)            |     |

| Figure 21-4: SCI Parameter Register(SCI_PARAM)             | 205 |

| Figure 21-5: SCI Reset Register(SCI_RESET)                 | 205 |

| Figure 21-6: SCI Pin Register(SCI_PIN)                     | 206 |

| Figure 21-7: SCI Baud Rate Register (SCI_BAUD)             |     |

| Figure 21-8: SCI Status Register (SCI_STAT)                | 209 |

| Figure 21-9: SCI Control Register (SCI_CTRL)               | 213 |

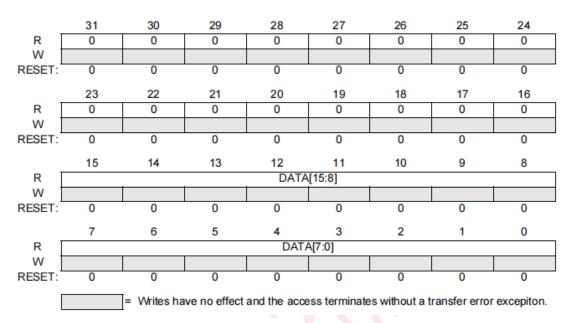

| Figure 21-10: SCI Data Register (SCI_DATA)                 | 217 |

| Figure 21-11: SCI Match Address Register (SCI_MATCH)       | 218 |

| Figure 21-12: SCI Modem IrDA Register (SCI_MODIR)          | 219 |

| Figure 21-13: SCI FIFO Register (SCI_FIFO)                 | 221 |

| Figure 21-14: SCI Watermark Register (SCI_WATER)           | 223 |

| Figure 21-15: SCI Oversampling Ratio Register (SCI_OSR)    | 224 |

| Figure 21-16: SCI Baud Rate Generation                     | 225 |

| Figure 22-1: SSI Block Diagram                             | 235 |

| Figure 22-2: Control Register 0(CTRLR0)                    | 237 |

| Figure 22-3: Control Register 1(CTRLR1)                    | 240 |

| Figure 22-4: SSI Enable Register(SSIENR)                   | 241 |

| Figure 22-5: Microwire Control Register(MWCR)              | 242 |

| Figure 22-6: Slave Enable Register(SER)                    | 243 |

| Figure 22-7: Baud Rate Select(BAUDR)                       | 244 |

| Figure 22-8: Transmit FIFO Threshold Level(TXFTLR)         | 245 |

| Figure 22-9: Receive FIFO Threshold Level(RXFTLR)          | 246 |

| Figure 22-10: Transmit FIFO Level Register(TXFLR)          | 247 |

| Figure 22-11: Receive FIFO Level Register(RXFLR)           | 247 |

| Figure 22-12: Status Register(SR)                          | 248 |

| Figure 22-13: Interrupt Mask Register(IMR)                 | 249 |

| Figure 22-14: Interrupt Status Register(ISR)                              | 250 |

|---------------------------------------------------------------------------|-----|

| Figure 22-15: Raw Interrupt Status Register(RISR)                         | 251 |

| Figure 22-16: Transmit FIFO Overflow Interrupt Clear Registers.(TXOICR)   | 252 |

| Figure 22-17: Receive FIFO Overflow Interrupt Clear Register(RXOICR)      | 253 |

| Figure 22-18: Receive FIFO Underflow Interrupt Clear Register(RXUICR)     | 253 |

| Figure 22-19: Interrupt Clear Register(ICR)                               | 254 |

| Figure 22-20: DMA Control Register(DMACR)                                 | 255 |

| Figure 22-21: DMA Transmit Data Level(DMATDLR)                            | 256 |

| Figure 22-22: DMA Receive Data Level(DMARDLR)                             | 257 |

| Figure 22-23: Identification Register(IDR)                                | 258 |

| Figure 22-24: Version ID Register(VIDR)                                   | 258 |

| Figure 22-25: SSI Data Register(DRx)                                      | 259 |

| Figure 22-26: RX Sample Delay Register (RXSDR)                            | 260 |

| Figure 22-27: SPI Control Register 0(SPICTRLR0)                           | 261 |

| Figure 22-28: XIP Mode Bits(XIPMBR)                                       | 262 |

| Figure 22-29: XIP Incr Inst Register(XIPIIR)                              | 263 |

| Figure 22-30: XIP Wrap Inst Register(XIPWIR)                              | 264 |

| Figure 22-31: XIP Control Register(XIPCR)                                 | 265 |

| Figure 22-32: XIP Slave Enable Register(XIPSER)                           | 267 |

| Figure 22-33: XIP Receive FIFO Overflow Interrupt Clear Register(XRXIOCR) | 268 |

| Figure 22-34: XIP Continues Transfer Time Out Register(XIPCTTOR)          | 269 |

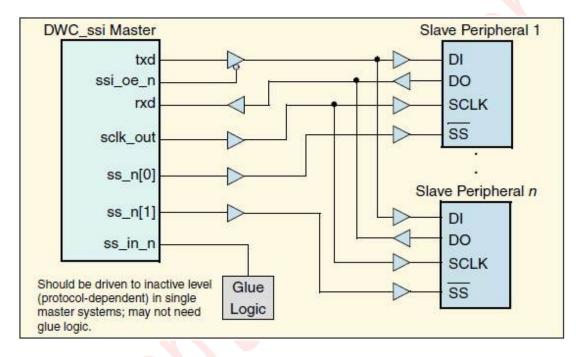

| Figure 22-35: SSI Configured as Master Device                             | 270 |

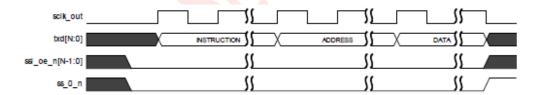

| Figure 22-36: Typical Write Operation Dual/Quad/Octal SPI Mode            | 272 |

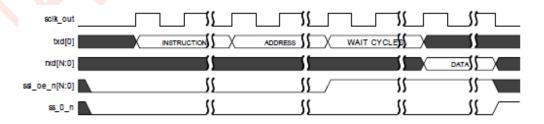

| Figure 22-37: Typical Read Operation Dual/Quad/Octal SPI Mode             | 272 |

| Figure 22-38: XIP Transfer with Instruction Phase                         | 273 |

| Figure 23-1: SPI Block Diagram                                            | 276 |

| Figure 23-2: SPI Control Register 1 (SPICR1)                              | 279 |

| Figure 23-3: SPI Control Register 2 (SPICR2)                              | 280 |

| Figure 23-4: SPI Baud Rate Register (SPIBR)                               |     |

| Figure 23-5: SPI Frame Register (SPIFR)                                   | 283 |

| Figure 23-6: SPI RX FIFO Control Register (SPIRXFCR)                      | 284 |

| Figure 23-7: SPI TX FIFO Control Register (SPITXFCR)                      | 284 |

| Figure 23-8: SPI RX FIFO TimeOut Counter Register (SPIRXFTOCTR)           |     |

| Figure 23-9: SPI TX FIFO TimeOut Counter Register (SPITXFTOCTR)           | 286 |

| Figure 23-10: SPI Port Data Direction Register (SPIDDR)                   | 286 |

| Figure 23-11: SPI Pullup and Reduced Drive Register (SPIPURD)             | 287 |

| Figure 23-12: SPI After SCK Delay Register (SPIASCDR)                     | 288 |

| Figure 23-13: SPI Before SCK Delay Register (SPIBSCDR)                    |     |

| Figure 23-14: SPI Port Data Register (SPIPORT)                            |     |

| Figure 23-15: SPI Transmit Counter Register (SPITCNT)                     |     |

| Figure 23-16: SPI Data Register (SPIDR)                                   |     |

|                                                                           |     |

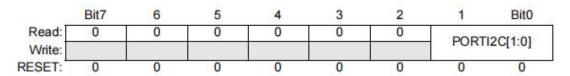

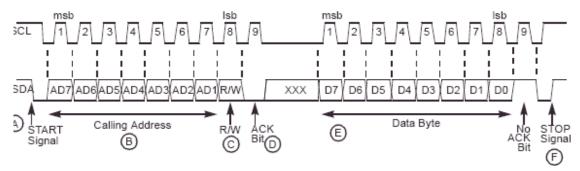

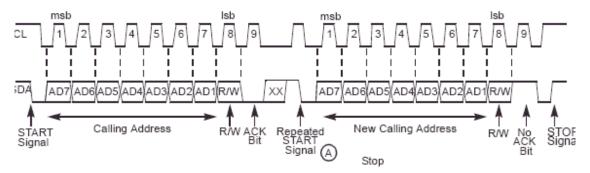

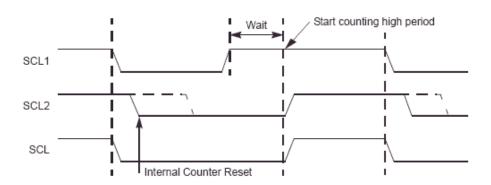

| Figure 23-18: SPI RX FIFO Status Register (SPIRXFSR)         29/5           Figure 23-20: SPI TX FIFO Status Register (SPITXFSR)         29/5           Figure 23-20: SPI DMA Control Register (SPIDMACR)         29/5           Figure 23-21: SPI DMA Threshold Register (SPIDMATHR)         29/6           Figure 23-22: SPI FIFO Debug Control Register (SPIRXFDBGR)         29/6           Figure 23-23: SPI Interrupt Control Register (SPIRXFDBGR)         29/6           Figure 23-26: Full-Duplex Operation         29/6           Figure 23-26: Full-Duplex Operation         29/6           Figure 23-27: SPI Clock Format 1 (CPHA = 1)         29/6           Figure 23-28: SPI Clock Format 0 (CPHA = 0)         30/7           Figure 23-29: Transmission Error Due to Master/Slave Clock Skew         30/7           Figure 23-30: Ti Single Transfer         30/7           Figure 23-31: Ti Continuous Transfer         30/7           Figure 24-1: 12C Block Diagram         30/7           Figure 24-2: 12C Status Register (I2CS)         31/7           Figure 24-3: 12C Clock Prescalar Register (I2CP)         31/7           Figure 24-4: 12C Control Register (I2CC)         31/7           Figure 24-6: 12C Port Control Register (I2CPCR)         31/7           Figure 24-7: 12C Slave High-Speed Mode Indicator Register (I2CSHIR)         31/7           Figure 24-8: 12C Port Da                                                | Figure 23-17: SPI Status Register (SPISR)                          | 290 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----|

| Figure 23-20: SPI DMA Control Register (SPIDMACR)         29           Figure 23-21: SPI DMA Threshold Register (SPIDMATHR)         29           Figure 23-22: SPI FIFO Debug Control Register (SPIEDCR)         29           Figure 23-23: SPI Interrupt Control Register (SPIENCR)         29           Figure 23-24: SPI RX FIFO Debug Register (SPIENXFDBGR)         296           Figure 23-25: SPI TX FIFO Debug Register (SPITXFDBGR)         296           Figure 23-26: Full-Duplex Operation         296           Figure 23-27: SPI Clock Format 1 (CPHA = 1)         296           Figure 23-28: SPI Clock Format 0 (CPHA = 0)         30           Figure 23-29: Transmission Error Due to Master/Slave Clock Skew         30           Figure 23-30: TI Single Transfer         30           Figure 23-31: TI Continuous Transfer         30           Figure 24-1: I2C Block Diagram         30           Figure 24-1: I2C Slock Register (I2CS)         31           Figure 24-2: I2C Status Register (I2CS)         31           Figure 24-3: I2C Clock Prescalar Register (I2CP)         31           Figure 24-4: I2C Control Register (I2CC)         31           Figure 24-6: I2C Port Control Register (I2CSA)         31           Figure 24-6: I2C Port Direction Register (I2CDDR)         31           Figure 24-10: I2C Port Direction Register (I2CDDR)         31                                                                | Figure 23-18: SPI RX FIFO Status Register (SPIRXFSR)               | 292 |

| Figure 23-21: SPI DMA Threshold Register (SPIDMATHR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figure 23-19: SPI TX FIFO Status Register (SPITXFSR)               | 293 |

| Figure 23-22: SPI FIFO Debug Control Register (SPIFDCR)         296           Figure 23-23: SPI Interrupt Control Register (SPIICR)         296           Figure 23-24: SPI RX FIFO Debug Register (SPIRXFDBGR)         298           Figure 23-25: Full-Duplex Operation         298           Figure 23-26: Full-Duplex Operation         298           Figure 23-27: SPI Clock Format 1 (CPHA = 1)         298           Figure 23-28: SPI Clock Format 0 (CPHA = 0)         300           Figure 23-39: Transmission Error Due to Master/Slave Clock Skew         301           Figure 23-30: TI Single Transfer         302           Figure 23-31: TI Continuous Transfer         303           Figure 23-32: High Speed Mode (CPHA = 0)         304           Figure 24-3: 12 Clock Prescalar Register (I2CO)         304           Figure 24-1: 12C Block Diagram         300           Figure 24-2: 12C Status Register (I2CO)         311           Figure 24-3: 12C Clock Prescalar Register (I2CO)         311           Figure 24-4: 12C Control Register (I2CO)         314           Figure 24-5: 12C Slave Address Register (I2CSA)         314           Figure 24-6: 12C Port Control Register (I2CDR)         314           Figure 24-7: 12C Slave High-Speed Mode Indicator Register (I2CSHT)         314           Figure 24-10: 12C Port Direction Register (I2CDR)         316                                                         | Figure 23-20: SPI DMA Control Register (SPIDMACR)                  | 293 |

| Figure 23-23: SPI Interrupt Control Register (SPIRCR)         298           Figure 23-24: SPI RX FIFO Debug Register (SPIRXFDBGR)         298           Figure 23-25: SPI TX FIFO Debug Register (SPITXFDBGR)         298           Figure 23-26: Full-Duplex Operation         298           Figure 23-27: SPI Clock Format 1 (CPHA = 1)         298           Figure 23-28: SPI Clock Format 0 (CPHA = 0)         300           Figure 23-39: Transmission Error Due to Master/Slave Clock Skew         300           Figure 23-30: TI Single Transfer         302           Figure 23-31: TI Continuous Transfer         302           Figure 23-32: High Speed Mode (CPHA = 0)         304           Figure 24-1: I2C Block Diagram         306           Figure 24-2: I2C Status Register(I2CS)         311           Figure 24-3: I2C Clock Prescalar Register (I2CP)         31-           Figure 24-4: I2C Control Register (I2CC)         31-           Figure 24-5: I2C Slave Address Register (I2CSA)         31-           Figure 24-6: I2C Port Control Register (I2CPCR)         31-           Figure 24-7: I2C Slave High-Speed Mode Indicator Register(I2CSHR)         31-           Figure 24-8: I2C Slave High-Speed Mode Indicator Register(I2CSHR)         31-           Figure 24-10: I2C Port Data Register (I2CDDR)         31-           Figure 24-11: I2C Communication Protocol                                                     | Figure 23-21: SPI DMA Threshold Register (SPIDMATHR)               | 294 |

| Figure 23-24: SPI RX FIFO Debug Register (SPIRXFDBGR)       296         Figure 23-25: SPI TX FIFO Debug Register (SPITXFDBGR)       296         Figure 23-27: Full-Duplex Operation       296         Figure 23-27: SPI Clock Format 1 (CPHA = 1)       296         Figure 23-28: SPI Clock Format 0 (CPHA = 0)       306         Figure 23-29: Transmission Error Due to Master/Slave Clock Skew       307         Figure 23-30: TI Single Transfer       307         Figure 23-31: TI Continuous Transfer       307         Figure 23-32: High Speed Mode (CPHA = 0)       309         Figure 24-1: 12C Block Diagram       309         Figure 24-2: 12C Status Register (I2CS)       301         Figure 24-3: 12C Clock Prescalar Register (I2CP)       311         Figure 24-4: 12C Control Register (I2CC)       312         Figure 24-5: 12C Slave Address Register (I2CP)       314         Figure 24-6: 12C Port Control Register (I2CPCR)       314         Figure 24-7: 12C Slave High-Speed Mode Indicator Register(I2CSHIR)       315         Figure 24-8: 12C Slave SDA Hold Time Register (I2CSHT)       316         Figure 24-9: 12C Data Register (I2CDDR)       316         Figure 24-10: 12C Port Data Register (I2CDDR)       316         Figure 24-11: 12C Communication Protocol       316         Figure 24-12: 12C Communication                                                                                                       | Figure 23-22: SPI FIFO Debug Control Register (SPIFDCR)            | 294 |

| Figure 23-25: SPI TX FIFO Debug Register (SPITXFDBGR)         296           Figure 23-26: Full-Duplex Operation         296           Figure 23-27: SPI Clock Format 1 (CPHA = 1)         298           Figure 23-28: SPI Clock Format 0 (CPHA = 0)         300           Figure 23-39: Transmission Error Due to Master/Slave Clock Skew         300           Figure 23-30: TI Single Transfer         300           Figure 23-31: TI Continuous Transfer         300           Figure 23-32: High Speed Mode (CPHA = 0)         300           Figure 24-1: I2C Block Diagram         300           Figure 24-2: I2C Status Register (I2CS)         310           Figure 24-3: I2C Clock Prescalar Register (I2CP)         311           Figure 24-4: I2C Control Register (I2CSA)         312           Figure 24-5: I2C Slave Address Register (I2CSA)         314           Figure 24-6: I2C Port Control Register (I2CPCR)         314           Figure 24-6: I2C Slave BDA Hold Time Register (I2CSHT)         315           Figure 24-9: I2C Data Register (I2CD)         316           Figure 24-10: I2C Port Direction Register (I2CDDR)         316           Figure 24-11: I2C Ort Data Register (I2CDDR)         317           Figure 24-12: I2C Communication Protocol         316           Figure 24-13: Repeat Start Of I2C Protocol         316 <td< td=""><td>Figure 23-23: SPI Interrupt Control Register (SPIICR)</td><td>295</td></td<> | Figure 23-23: SPI Interrupt Control Register (SPIICR)              | 295 |

| Figure 23-26: Full-Duplex Operation       296         Figure 23-27: SPI Clock Format 1 (CPHA = 1)       296         Figure 23-28: SPI Clock Format 0 (CPHA = 0)       300         Figure 23-29: Transmission Error Due to Master/Slave Clock Skew       301         Figure 23-30: TI Single Transfer       302         Figure 23-31: TI Continuous Transfer       302         Figure 23-32: High Speed Mode (CPHA = 0)       304         Figure 24-1: I2C Block Diagram       309         Figure 24-1: I2C Status Register (I2CS)       310         Figure 24-2: I2C Status Register (I2CC)       311         Figure 24-3: I2C Clock Prescalar Register (I2CSA)       312         Figure 24-4: I2C Control Register (I2CPCR)       313         Figure 24-5: I2C Slave Address Register (I2CPCR)       314         Figure 24-6: I2C Port Control Register (I2CPCR)       314         Figure 24-6: I2C Slave High-Speed Mode Indicator Register (I2CSHIR)       314         Figure 24-8: I2C Slave SDA Hold Time Register (I2CPCR)       314         Figure 24-9: I2C Data Register (I2CDD)       316         Figure 24-10: I2C Port Direction Register (I2CDDR)       316         Figure 24-11: I2C Communication Protocol       316         Figure 24-12: I2C Communication       320         Figure 24-13: Repeat Start Of I2C Protocol       316                                                                                                            | Figure 23-24: SPI RX FIFO Debug Register (SPIRXFDBGR)              | 295 |

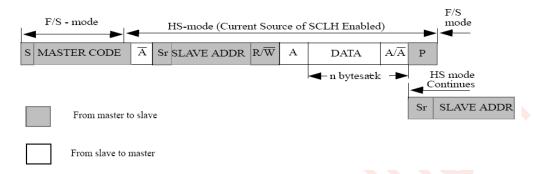

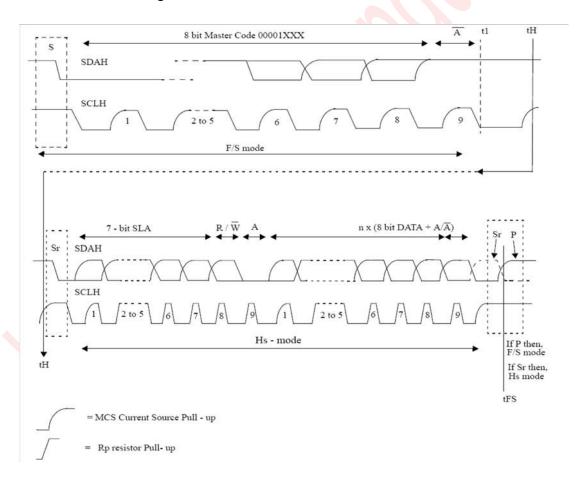

| Figure 23-27: SPI Clock Format 1 (CPHA = 1)       298         Figure 23-28: SPI Clock Format 0 (CPHA = 0)       300         Figure 23-39: Transmission Error Due to Master/Slave Clock Skew       300         Figure 23-30: TI Single Transfer       300         Figure 23-31: TI Continuous Transfer       300         Figure 23-31: TI Speed Mode (CPHA = 0)       300         Figure 24-1: 12C Block Diagram       300         Figure 24-1: 12C Block Diagram       301         Figure 24-2: 12C Status Register (12CS)       311         Figure 24-3: 12C Clock Prescalar Register (12CP)       311         Figure 24-4: 12C Control Register (12CC)       312         Figure 24-5: 12C Slave Address Register (12CSA)       313         Figure 24-6: 12C Port Control Register (12CPCR)       314         Figure 24-7: 12C Slave High-Speed Mode Indicator Register(12CSHIR)       314         Figure 24-8: 12C Slave SDA Hold Time Register(12CSHT)       315         Figure 24-9: 12C Data Register(12CD)       316         Figure 24-10: 12C Port Direction Register (12CPDR)       317         Figure 24-11: 12C Port Data Register (12CPDR)       317         Figure 24-12: 12C Communication Protocol       318         Figure 24-13: Repeat Start Of 12C Protocol       316         Figure 24-16: A Complete HS Mode Transfer       32                                                                                                            | Figure 23-25: SPI TX FIFO Debug Register (SPITXFDBGR)              | 296 |